Jinghe Wang

Learning with Challenges: Adaptive Difficulty-Aware Data Generation for Mobile GUI Agent Training

Jan 30, 2026Abstract:Large-scale, high-quality interaction trajectories are essential for advancing mobile Graphical User Interface (GUI) agents. While existing methods typically rely on labor-intensive human demonstrations or automated model exploration to generate GUI trajectories, they lack fine-grained control over task difficulty. This fundamentally restricts learning effectiveness due to the mismatch between the training difficulty and the agent's capabilities. Inspired by how humans acquire skills through progressively challenging tasks, we propose MobileGen, a novel data generation framework that adaptively aligns training difficulty with the GUI agent's capability frontier. Specifically, MobileGen explicitly decouples task difficulty into structural (e.g., trajectory length) and semantic (e.g., task goal) dimensions. It then iteratively evaluates the agent on a curated prior dataset to construct a systematic profile of its capability frontier across these two dimensions. With this profile, the probability distribution of task difficulty is adaptively computed, from which the target difficulty for the next round of training can be sampled. Guided by the sampled difficulty, a multi-agent controllable generator is finally used to synthesize high-quality interaction trajectories along with corresponding task instructions. Extensive experiments show that MobileGen consistently outperforms existing data generation methods by improving the average performance of GUI agents by 1.57 times across multiple challenging benchmarks. This highlights the importance of capability-aligned data generation for effective mobile GUI agent training.

CoBel-World: Harnessing LLM Reasoning to Build a Collaborative Belief World for Optimizing Embodied Multi-Agent Collaboration

Sep 26, 2025

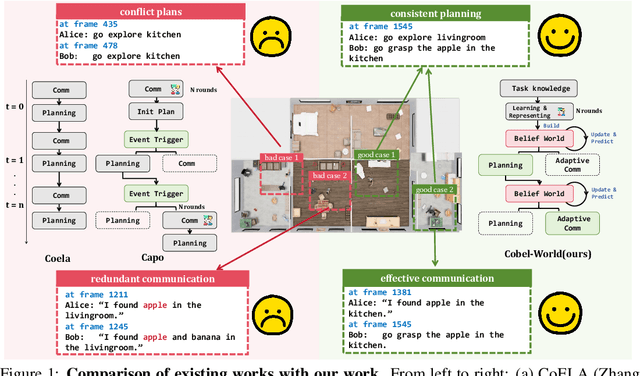

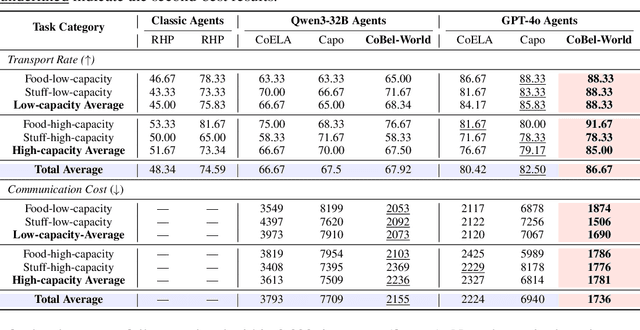

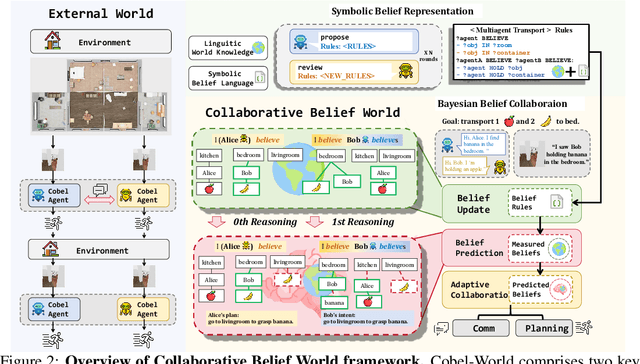

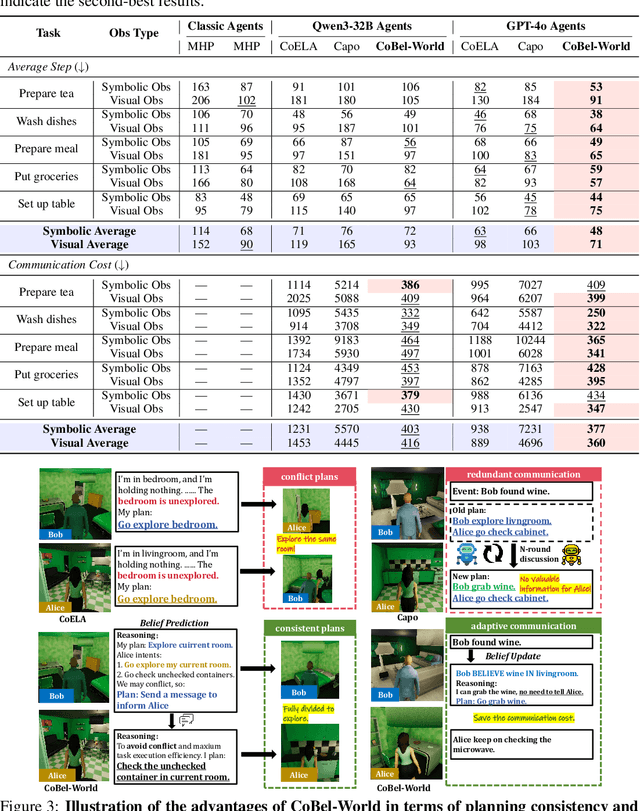

Abstract:Effective real-world multi-agent collaboration requires not only accurate planning but also the ability to reason about collaborators' intents -- a crucial capability for avoiding miscoordination and redundant communication under partial observable environments. Due to their strong planning and reasoning capabilities, large language models (LLMs) have emerged as promising autonomous agents for collaborative task solving. However, existing collaboration frameworks for LLMs overlook their reasoning potential for dynamic intent inference, and thus produce inconsistent plans and redundant communication, reducing collaboration efficiency. To bridge this gap, we propose CoBel-World, a novel framework that equips LLM agents with a collaborative belief world -- an internal representation jointly modeling the physical environment and collaborators' mental states. CoBel-World enables agents to parse open-world task knowledge into structured beliefs via a symbolic belief language, and perform zero-shot Bayesian-style belief updates through LLM reasoning. This allows agents to proactively detect potential miscoordination (e.g., conflicting plans) and communicate adaptively. Evaluated on challenging embodied benchmarks (i.e., TDW-MAT and C-WAH), CoBel-World significantly reduces communication costs by 22-60% and improves task completion efficiency by 4-28% compared to the strongest baseline. Our results show that explicit, intent-aware belief modeling is essential for efficient and human-like collaboration in LLM-based multi-agent systems.

CATP-LLM: Empowering Large Language Models for Cost-Aware Tool Planning

Nov 25, 2024Abstract:Utilizing large language models (LLMs) for tool planning has emerged as a promising avenue for developing general AI systems, where LLMs automatically schedule external tools (e.g. vision models) to tackle complex tasks based on task descriptions. To push this paradigm toward practical applications, it is crucial for LLMs to consider tool execution costs (e.g. execution time) for tool planning. Unfortunately, prior studies overlook the tool execution costs, leading to the generation of expensive plans of which the costs outweigh task performance. To fill this gap, we propose the Cost-Aware Tool Planning with LLMs (CATP-LLM) framework, which for the first time provides a coherent design to empower LLMs for cost-aware tool planning. Specifically, CATP-LLM incorporates a tool planning language to enhance the LLM to generate non-sequential plans of multiple branches for efficient concurrent tool execution and cost reduction. Moreover, it further designs a cost-aware offline reinforcement learning algorithm to fine-tune the LLM to optimize the performance-cost trade-off in tool planning. In lack of public cost-related datasets, we further present OpenCATP, the first platform for cost-aware planning evaluation. Experiments on OpenCATP show that CATP-LLM outperforms GPT-4 even when using Llama2-7B as its backbone, with the average improvement of 28.2%-30.2% higher plan performance and 24.7%-45.8% lower costs even on the challenging planning tasks. The codes of CATP-LLM and OpenCATP will be publicly available.

Rotatable Block-Controlled RIS: Bridging the Performance Gap to Element-Controlled Systems

Aug 22, 2024

Abstract:The passive reconfigurable intelligent surface (RIS) requires numerous elements to achieve adequate array gain, which linearly increases power consumption (PC) with the number of reflection phases. To address this, this letter introduces a rotatable block-controlled RIS (BC-RIS) that preserves spectral efficiency (SE) while reducing power costs. Unlike the element-controlled RIS (EC-RIS), which necessitates independent phase control for each element, the BC-RIS uses a single phase control circuit for each block, substantially lowering power requirements. In the maximum ratio transmission, by customizing specular reflection channels through the rotation of blocks and coherently superimposing signals with optimized reflection phase of blocks, the BC-RIS achieves the same averaged SE as the EC-RIS. To counteract the added power demands from rotation, influenced by block size, we have developed a segmentation scheme to minimize overall PC. Furthermore, constraints for rotation power-related parameters have been established to enhance the energy efficiency of the BC-RIS compared to the EC-RIS. Numerical results confirm that this approach significantly improves energy efficiency while maintaining performance.

Static Power Consumption Modeling and Measurement of Reconfigurable Intelligent Surfaces

Mar 01, 2023

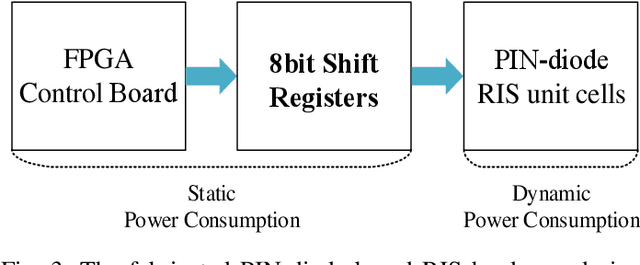

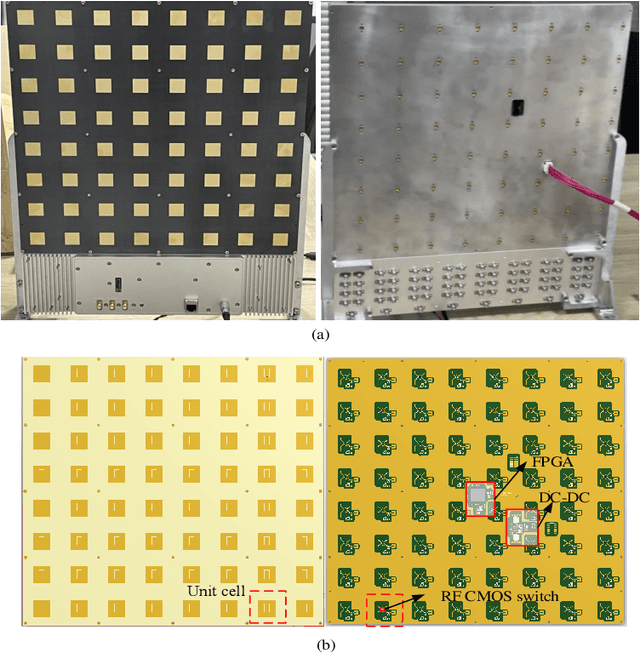

Abstract:Reconfigurable intelligent surfaces (RISs) are anticipated to transform wireless communication in a way that is both economical and energy efficient. Revealing the practical power consumption characteristics of RISs can provide an essential toolkit for the optimal design of RIS-assisted wireless communication systems and energy efficiency performance evaluation. Based on our previous work that modeled the dynamic power consumption of RISs, we henceforth concentrate more on static power consumption. We first divide the RIS hardware into three basic parts: the FPGA control board, the drive circuits, and the RIS unit cells. The first two parts are mainly to be investigated and the last part has been modeled as the dynamic power consumption in the previous work. In this work, the power consumption of the FPGA control board is regarded as a constant value, however, that of the drive circuit is a variant that is affected by the number of control signals and its self-power consumption characteristics. Therefore, we model the power consumption of the drive circuits of various kinds of RISs, i.e., PIN diode-/Varactor diode-/RF switch-based RIS. Finally, the measurement results and typical value of static power consumption are illustrated and discussed.

Reconfigurable Intelligent Surface: Power Consumption Modeling and Practical Measurement Validation

Nov 01, 2022

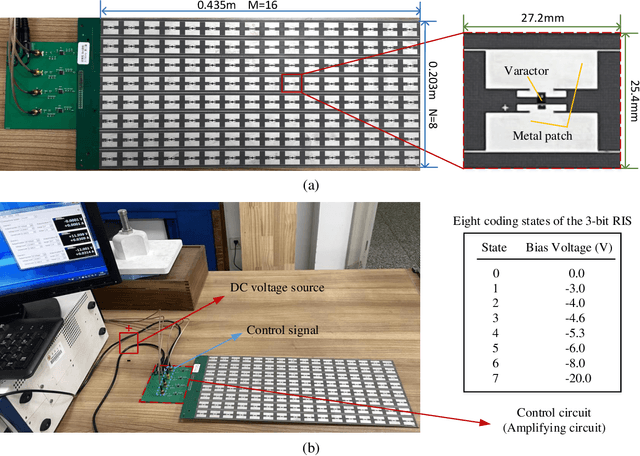

Abstract:Due to the ability to reshape the wireless communication environment in a cost- and energy-efficient manner, the reconfigurable intelligent surface (RIS) has garnered substantial attention. However, the explicit power consumption model of RIS and measurement validation, have received far too little attention. Therefore, in this work, we propose the RIS power consumption model and implement the practical measurement validation with various RISs. Measurement results illustrate the generality and accuracy of the proposed model. Firstly, we verify that RIS has static power consumption, and present the experiment results. Secondly, we confirm that the dynamic power consumption of the varactor-diode based RIS is almost negligible. Finally but significantly, we model the quantitative relationship between the dynamic power consumption of the PIN-diode based RIS and the polarization mode, controllable bit resolution, working status of RIS, which is validated by practical experimental results.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge