Bhavin J. Shastri

Dynamic Electro-Optic Analog Memory for Neuromorphic Photonic Computing

Jan 29, 2024

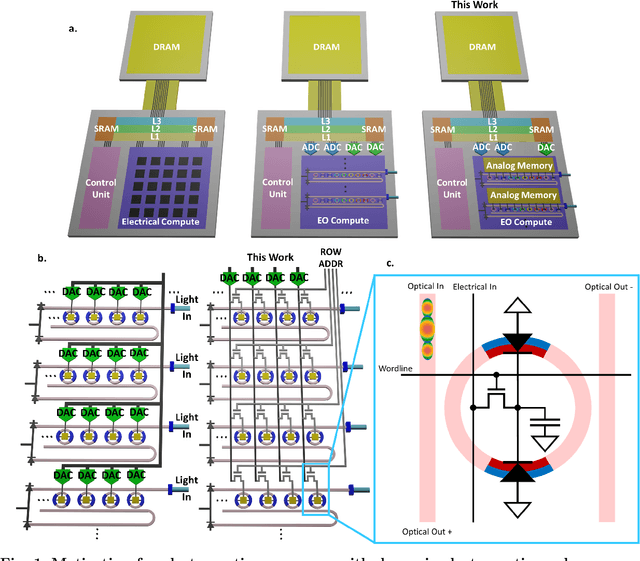

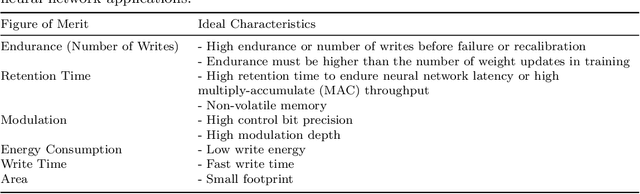

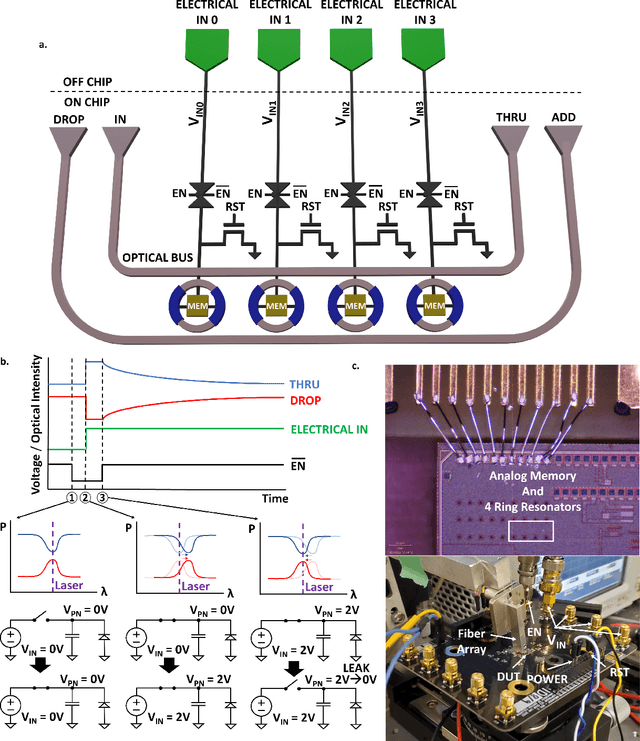

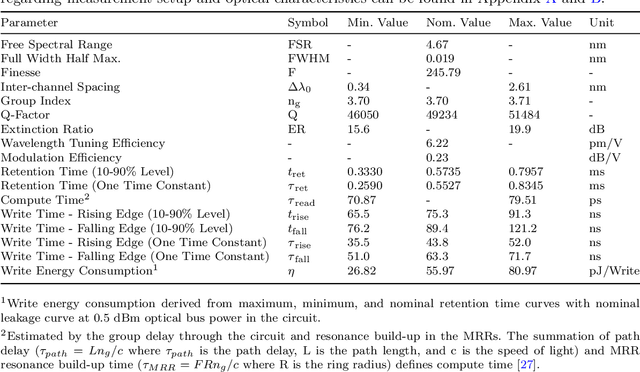

Abstract:Artificial intelligence (AI) has seen remarkable advancements across various domains, including natural language processing, computer vision, autonomous vehicles, and biology. However, the rapid expansion of AI technologies has escalated the demand for more powerful computing resources. As digital computing approaches fundamental limits, neuromorphic photonics emerges as a promising platform to complement existing digital systems. In neuromorphic photonic computing, photonic devices are controlled using analog signals. This necessitates the use of digital-to-analog converters (DAC) and analog-to-digital converters (ADC) for interfacing with these devices during inference and training. However, data movement between memory and these converters in conventional von Neumann computing architectures consumes energy. To address this, analog memory co-located with photonic computing devices is proposed. This approach aims to reduce the reliance on DACs and ADCs and minimize data movement to enhance compute efficiency. This paper demonstrates a monolithically integrated neuromorphic photonic circuit with co-located capacitive analog memory and compares various analog memory technologies for neuromorphic photonic computing using the MNIST dataset as a benchmark.

A system-on-chip microwave photonic processor solves dynamic RF interference in real time with picosecond latency

Jun 26, 2023Abstract:Radio-frequency interference is a growing concern as wireless technology advances, with potentially life-threatening consequences like interference between radar altimeters and 5G cellular networks. Mobile transceivers mix signals with varying ratios over time, posing challenges for conventional digital signal processing (DSP) due to its high latency. These challenges will worsen as future wireless technologies adopt higher carrier frequencies and data rates. However, conventional DSPs, already on the brink of their clock frequency limit, are expected to offer only marginal speed advancements. This paper introduces a photonic processor to address dynamic interference through blind source separation (BSS). Our system-on-chip processor employs a fully integrated photonic signal pathway in the analogue domain, enabling rapid demixing of received mixtures and recovering the signal-of-interest in under 15 picoseconds. This reduction in latency surpasses electronic counterparts by more than three orders of magnitude. To complement the photonic processor, electronic peripherals based on field-programmable gate array (FPGA) assess the effectiveness of demixing and continuously update demixing weights at a rate of up to 305 Hz. This compact setup features precise dithering weight control, impedance-controlled circuit board and optical fibre packaging, suitable for handheld and mobile scenarios. We experimentally demonstrate the processor's ability to suppress transmission errors and maintain signal-to-noise ratios in two scenarios, radar altimeters and mobile communications. This work pioneers the real-time adaptability of integrated silicon photonics, enabling online learning and weight adjustments, and showcasing practical operational applications for photonic processing.

Real-Time Blind Photonic Interference Cancellation for mmWave MIMO

May 06, 2023Abstract:Multiple-input multiple-output (MIMO) mmWave devices broadcast multiple spatially-separated data streams simultaneously in order to increase data transfer rates. Data transfer can, however, be compromised by interference. Conventional techniques for mitigating interference require additional space and power not generally available in handheld mobile devices. Here, we propose a photonic mmWave MIMO receiver architecture capable of interference cancellation with greatly reduced space and power needs. We demonstrate real-time photonic interference cancellation with an integrated FPGA-photonic system that executes a novel zero-calibration micro-ring resonator control algorithm. The system achieves sub-second cancellation weight determination latency with sub-Nyquist sampling. We evaluate the impact of canceller design parameters on performance, establishing that effective photonic cancellation is possible in handheld devices with less than 30 ms weight determination latency.

Interfacing spiking VCSEL-neurons with silicon photonics weight banks towards integrated neuromorphic photonic systems

May 01, 2023Abstract:Spiking neurons and neural networks constitute a fundamental building block for brain-inspired computing, which is posed to benefit significantly from photonic hardware implementations. In this work, we experimentally investigate an interconnected system based on an ultrafast spiking VCSEL-neuron and a silicon photonics (SiPh) integrated micro-ring resonator (MRR) weight bank, and demonstrate two different functional arrangements of these devices. First, we show that MRR weightbanks can be used in conjuction with the spiking VCSEL-neurons to perform amplitude weighting of sub-ns optical spiking signals. Second, we show that a continuous firing VCSEL-neuron can be directly modulated using a locking signal propagated through a single weighting micro-ring, and we utilize this functionality to perform optical spike firing rate-coding via thermal tuning of the micro-ring resonator. Given the significant track record of both integrated weight banks and photonic VCSEL-neurons, we believe these results demonstrate the viability of combining these two classes of devices for use in functional neuromorphic photonic systems.

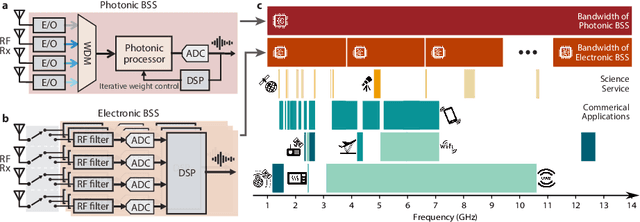

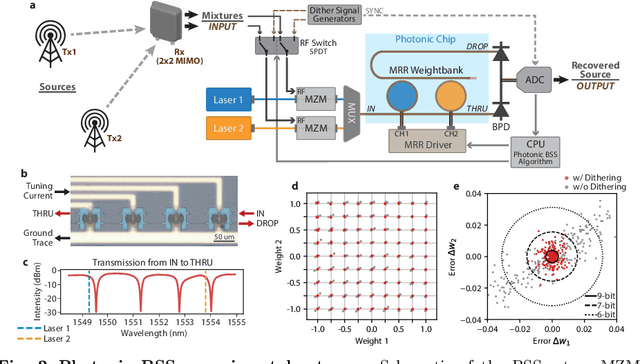

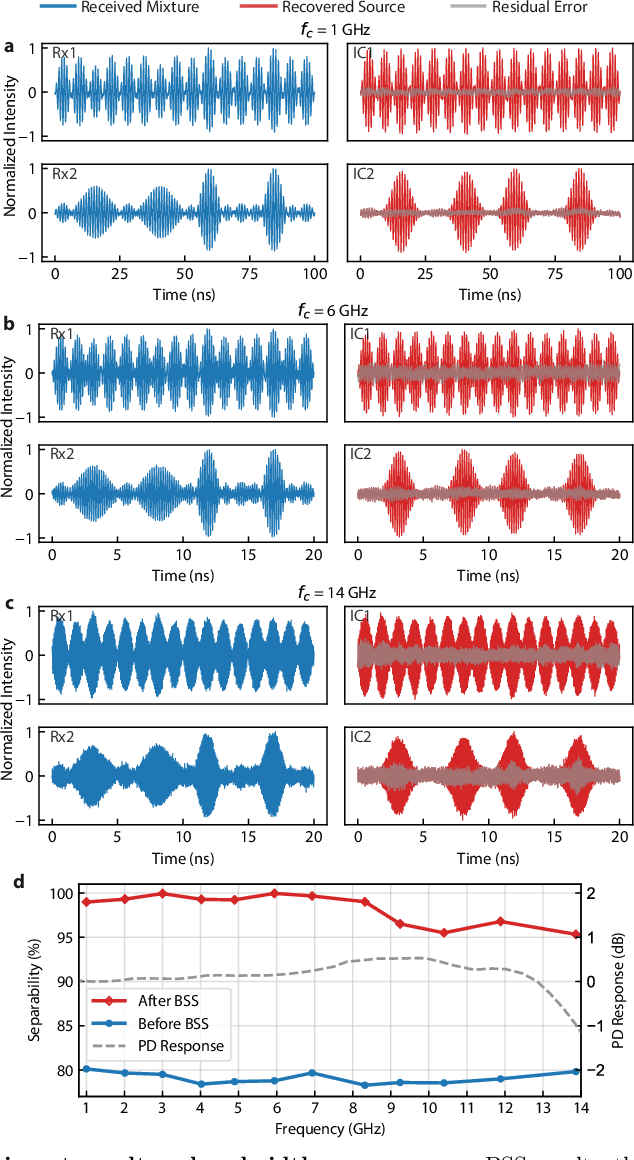

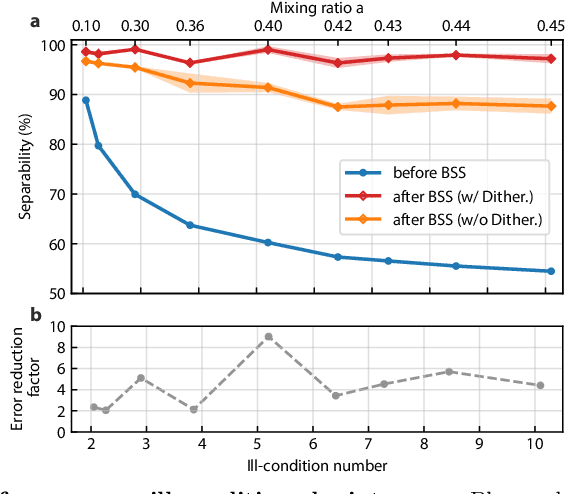

Wideband physical layer cognitive radio with an integrated photonic processor for blind source separation

May 17, 2022

Abstract:The expansion of telecommunications incurs increasingly severe crosstalk and interference, and a physical layer cognitive method, called blind source separation (BSS), can effectively address these issues. BSS requires minimal prior knowledge to recover signals from their mixtures, agnostic to carrier frequency, signal format, and channel conditions. However, the previous BSS implemented in electronics did not fulfill this versatility due to the inherently narrow bandwidth of radio-frequency (RF) components, the high energy consumption of digital signal processors (DSP), and their shared weaknesses of low scalability. Here, we report a photonic BSS approach that inherits the advantages of optical devices and can fully fulfill its "blindness" aspect. Using a microring weight bank integrated on a photonic chip, we demonstrate energy-efficient, WDM-scalable BSS across 13.8 GHz of bandwidth, covering many standard frequency bands. Our system also has high (9-bit) accuracy for signal demixing thanks to a recently developed dithering control method, resulting in higher signal of interest ratios (SIR) even for ill-conditioned mixtures.

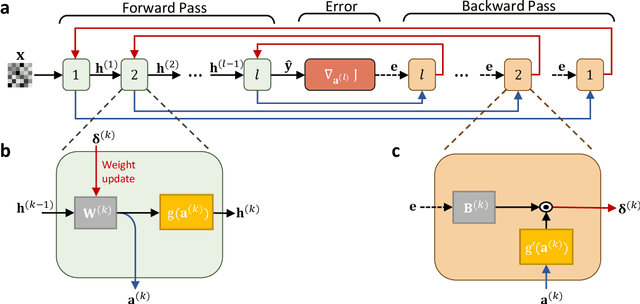

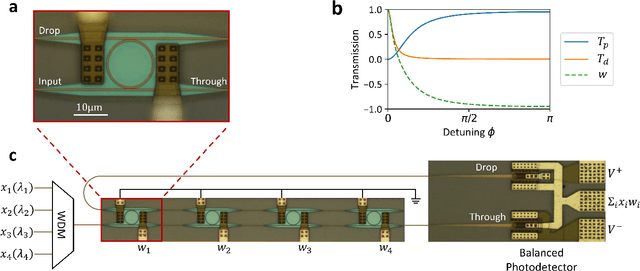

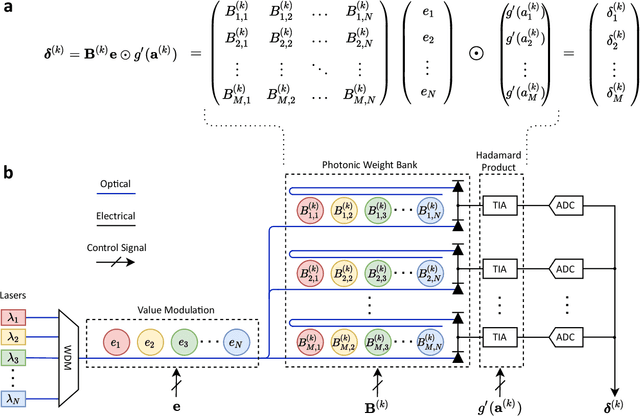

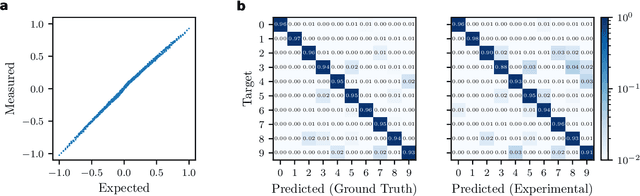

Monolithic Silicon Photonic Architecture for Training Deep Neural Networks with Direct Feedback Alignment

Nov 12, 2021

Abstract:The field of artificial intelligence (AI) has witnessed tremendous growth in recent years, however some of the most pressing challenges for the continued development of AI systems are the fundamental bandwidth, energy efficiency, and speed limitations faced by electronic computer architectures. There has been growing interest in using photonic processors for performing neural network inference operations, however these networks are currently trained using standard digital electronics. Here, we propose on-chip training of neural networks enabled by a CMOS-compatible silicon photonic architecture to harness the potential for massively parallel, efficient, and fast data operations. Our scheme employs the direct feedback alignment training algorithm, which trains neural networks using error feedback rather than error backpropagation, and can operate at speeds of trillions of multiply-accumulate (MAC) operations per second while consuming less than one picojoule per MAC operation. The photonic architecture exploits parallelized matrix-vector multiplications using arrays of microring resonators for processing multi-channel analog signals along single waveguide buses to calculate the gradient vector of each neural network layer in situ, which is the most computationally expensive operation performed during the backward pass. We also experimentally demonstrate training a deep neural network with the MNIST dataset using on-chip MAC operation results. Our novel approach for efficient, ultra-fast neural network training showcases photonics as a promising platform for executing AI applications.

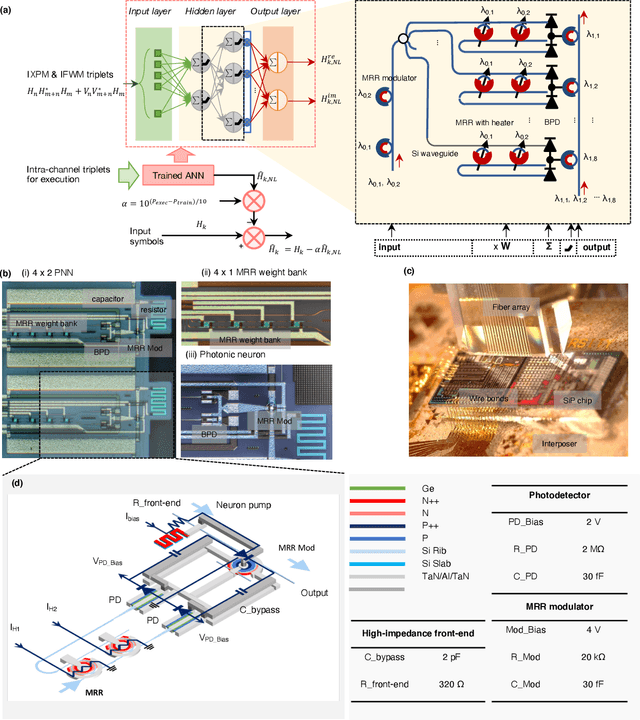

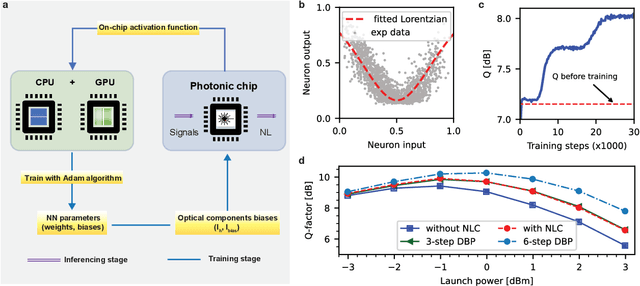

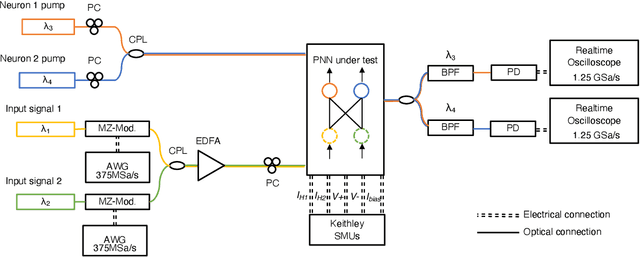

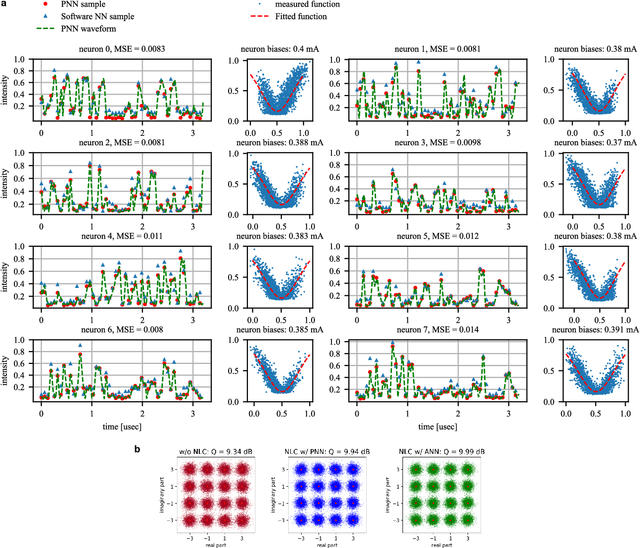

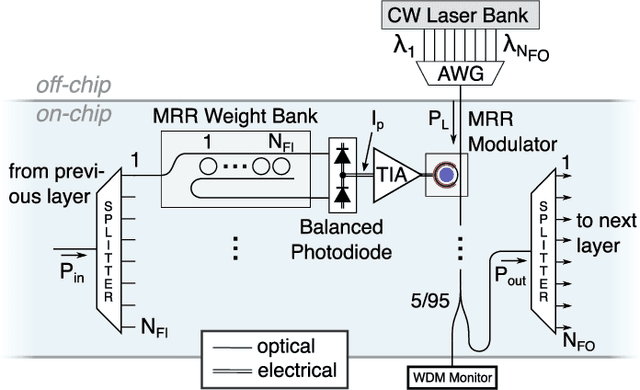

Silicon photonic-electronic neural network for fibre nonlinearity compensation

Oct 11, 2021

Abstract:In optical communication systems, fibre nonlinearity is the major obstacle in increasing the transmission capacity. Typically, digital signal processing techniques and hardware are used to deal with optical communication signals, but increasing speed and computational complexity create challenges for such approaches. Highly parallel, ultrafast neural networks using photonic devices have the potential to ease the requirements placed on the digital signal processing circuits by processing the optical signals in the analogue domain. Here we report a silicon photonice-lectronic neural network for solving fibre nonlinearity compensation of submarine optical fibre transmission systems. Our approach uses a photonic neural network based on wavelength-division multiplexing built on a CMOS-compatible silicon photonic platform. We show that the platform can be used to compensate optical fibre nonlinearities and improve the signal quality (Q)-factor in a 10,080 km submarine fibre communication system. The Q-factor improvement is comparable to that of a software-based neural network implemented on a 32-bit graphic processing unit-assisted workstation. Our reconfigurable photonic-electronic integrated neural network promises to address pressing challenges in high-speed intelligent signal processing.

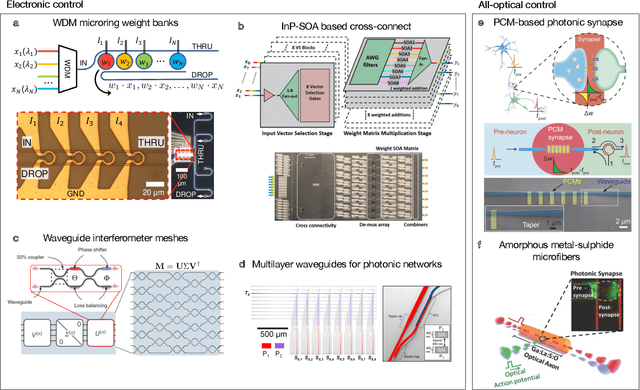

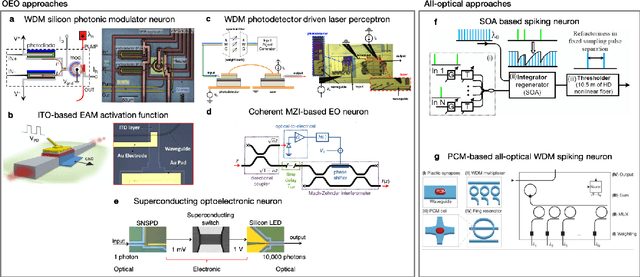

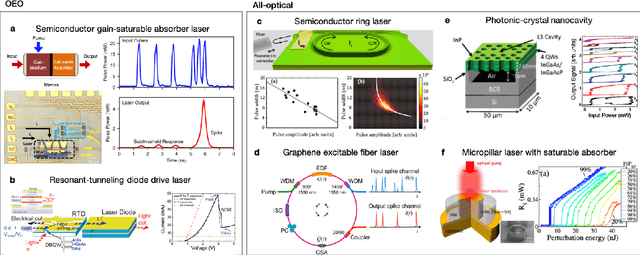

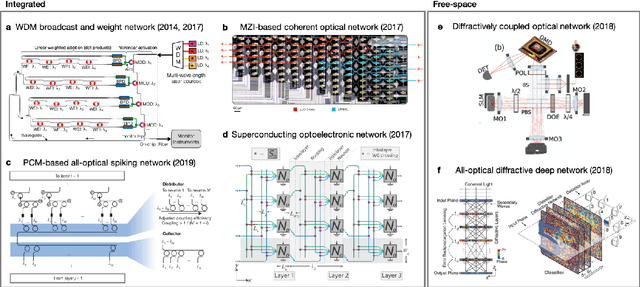

Photonics for artificial intelligence and neuromorphic computing

Nov 12, 2020

Abstract:Research in photonic computing has flourished due to the proliferation of optoelectronic components on photonic integration platforms. Photonic integrated circuits have enabled ultrafast artificial neural networks, providing a framework for a new class of information processing machines. Algorithms running on such hardware have the potential to address the growing demand for machine learning and artificial intelligence, in areas such as medical diagnosis, telecommunications, and high-performance and scientific computing. In parallel, the development of neuromorphic electronics has highlighted challenges in that domain, in particular, related to processor latency. Neuromorphic photonics offers sub-nanosecond latencies, providing a complementary opportunity to extend the domain of artificial intelligence. Here, we review recent advances in integrated photonic neuromorphic systems, discuss current and future challenges, and outline the advances in science and technology needed to meet those challenges.

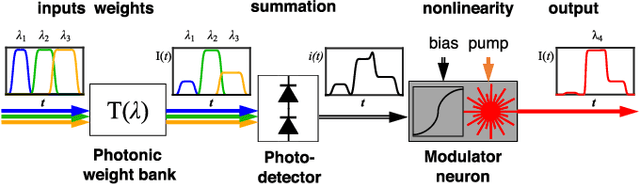

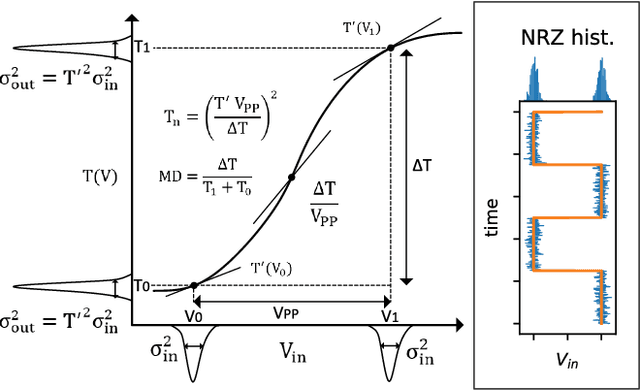

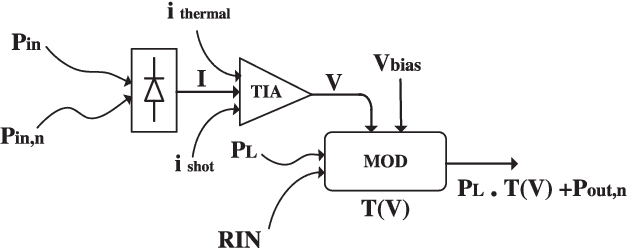

Noise Analysis of Photonic Modulator Neurons

Jul 17, 2019

Abstract:Neuromorphic photonics relies on efficiently emulating analog neural networks at high speeds. Prior work showed that transducing signals from the optical to the electrical domain and back with transimpedance gain was an efficient approach to implementing analog photonic neurons and scalable networks. Here, we examine modulator-based photonic neuron circuits with passive and active transimpedance gains, with special attention to the sources of noise propagation. We find that a modulator nonlinear transfer function can suppress noise, which is necessary to avoid noise propagation in hardware neural networks. In addition, while efficient modulators can reduce power for an individual neuron, signal-to-noise ratios must be traded off with power consumption at a system level. Active transimpedance amplifiers may help relax this tradeoff for conventional p-n junction silicon photonic modulators, but a passive transimpedance circuit is sufficient when very efficient modulators (i.e. low C and low V-pi) are employed.

Takens-inspired neuromorphic processor: a downsizing tool for random recurrent neural networks via feature extraction

Jul 06, 2019

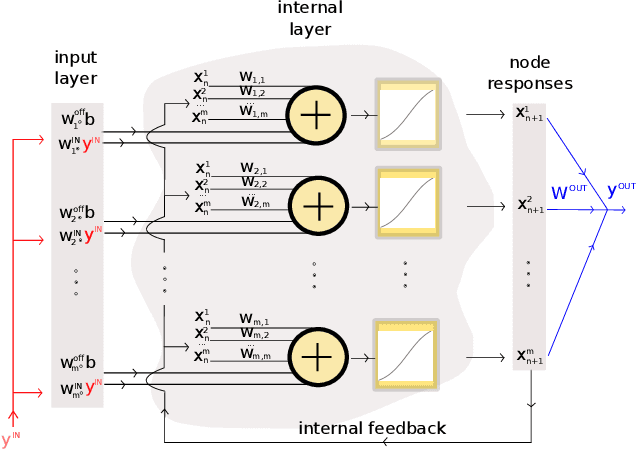

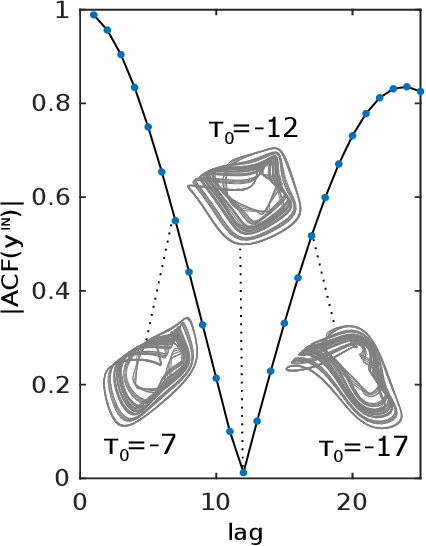

Abstract:We describe a new technique which minimizes the amount of neurons in the hidden layer of a random recurrent neural network (rRNN) for time series prediction. Merging Takens-based attractor reconstruction methods with machine learning, we identify a mechanism for feature extraction that can be leveraged to lower the network size. We obtain criteria specific to the particular prediction task and derive the scaling law of the prediction error. The consequences of our theory are demonstrated by designing a Takens-inspired hybrid processor, which extends a rRNN with a priori designed delay external memory. Our hybrid architecture is therefore designed including both, real and virtual nodes. Via this symbiosis, we show performance of the hybrid processor by stabilizing an arrhythmic neural model. Thanks to our obtained design rules, we can reduce the stabilizing neural network's size by a factor of 15 with respect to a standard system.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge