Shlomi Savariego

Practical Modulo Sampling: Mitigating High-Frequency Components

Jan 20, 2025

Abstract:Recovering signals within limited dynamic range (DR) constraints remains a central challenge for analog-to-digital converters (ADCs). To prevent data loss, an ADCs DR typically must exceed that of the input signal. Modulo sampling has recently gained attention as a promising approach for addressing DR limitations across various signal classes. However, existing methods often rely on ideal ADCs capable of capturing the high frequencies introduced by the modulo operator, which is impractical in real-world hardware applications. This paper introduces an innovative hardware-based sampling approach that addresses these high-frequency components using an analog mixer followed by a Low-Pass Filter (LPF). This allows the use of realistic ADCs, which do not need to handle frequencies beyond the intended sampling rate. Our method eliminates the requirement for high-specification ADCs and demonstrates that the resulting samples are equivalent to those from an ideal high-spec ADC. Consequently, any existing modulo recovery algorithm can be applied effectively. We present a practical hardware prototype of this approach, validated through both simulations and hardware recovery experiments. Using a recovery method designed to handle quantization noise, we show that our approach effectively manages high-frequency artifacts, enabling reliable modulo recovery with realistic ADCs. These findings confirm that our hardware solution not only outperforms conventional methods in high-precision settings but also demonstrates significant real-world applicability.

Robust Phantom-Assisted Framework for Multi-Person Localization and Vital Signs Monitoring Using MIMO FMCW Radar

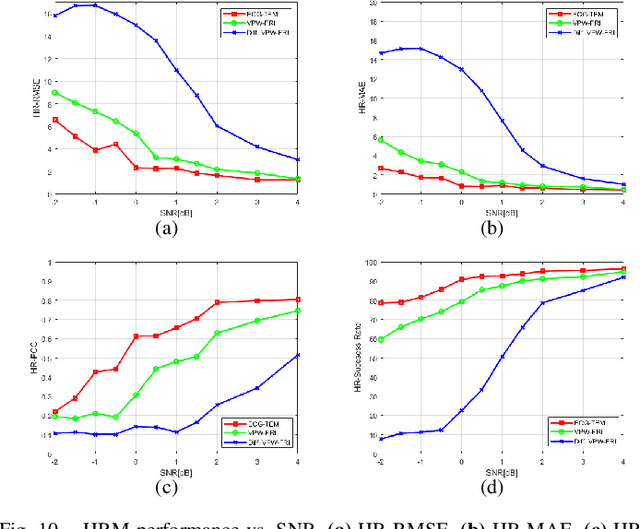

Jan 12, 2025Abstract:With the rising prevalence of cardiovascular and respiratory disorders and an aging global population, healthcare systems face increasing pressure to adopt efficient, non-contact vital sign monitoring (NCVSM) solutions. This study introduces a robust framework for multi-person localization and vital signs monitoring, using multiple-input-multiple-output frequency-modulated continuous wave radar, addressing challenges in real-world, cluttered environments. Two key contributions are presented. First, a custom hardware phantom was developed to simulate multi-person NCVSM scenarios, utilizing recorded thoracic impedance signals to replicate realistic cardiopulmonary dynamics. The phantom's design facilitates repeatable and rapid validation of radar systems and algorithms under diverse conditions to accelerate deployment in human monitoring. Second, aided by the phantom, we designed a robust algorithm for multi-person localization utilizing joint sparsity and cardiopulmonary properties, alongside harmonics-resilient dictionary-based vital signs estimation, to mitigate interfering respiration harmonics. Additionally, an adaptive signal refinement procedure is introduced to enhance the accuracy of continuous NCVSM by leveraging the continuity of the estimates. Performance was validated and compared to existing techniques through 12 phantom trials and 12 human trials, including both single- and multi-person scenarios, demonstrating superior localization and NCVSM performance. For example, in multi-person human trials, our method achieved average respiration rate estimation accuracies of 94.14%, 98.12%, and 98.69% within error thresholds of 2, 3, and 4 breaths per minute, respectively, and heart rate accuracies of 87.10%, 94.12%, and 95.54% within the same thresholds. These results highlight the potential of this framework for reliable multi-person NCVSM in healthcare and IoT applications.

ECG-TEM: Time-based sub-Nyquist sampling for ECG signal reconstruction and Hardware Prototype

May 22, 2024

Abstract:Portable heart rate monitoring (HRM) systems based on electrocardiograms (ECGs) have become increasingly crucial for preventing lifestyle diseases. For such portable systems, minimizing power consumption and sampling rate is critical due to the substantial data generated during long-term ECG monitoring. The variable pulse-width finite rate of innovation (VPW-FRI) framework provides an effective solution for low-rate sampling and compression of ECG signals. We develop a time-based sub-Nyquist sampling and reconstruction method for ECG signals specifically designed for HRM applications. Our approach harnesses the integrate-and-fire time-encoding machine (IF-TEM) as a power-efficient, time-based, asynchronous sampler, generating a sequence of time instants without the need for a global clock. The ECG signal is represented as a linear combination of VPW-FRI pulses, which is then subjected to pre-filtering before being sampled by the IF-TEM sampler. A compactly supported robust filter with a frequency-domain alias cancellation condition is used to combat the effects of noise. Our reconstruction process involves consecutive partial summations of discrete representations of the input signal derived from the series of time encodings, further enhancing the accuracy of the reconstructed ECG signals. Additionally, we introduce an IF-TEM sampling hardware system for ECG signals, implemented using an analog filter device. The firing rate is 42-80Hz, equivalent to approximately 0.025-0.05 of the Nyquist rate. Our hardware validation bridges the gap between theory and practice and demonstrates the robust performance and practical applicability of our approach in accurately monitoring heart rates and reconstructing ECG signals.

A Hardware Prototype of Wideband High-Dynamic Range ADC

Jan 29, 2023Abstract:Key parameters of analog-to-digital converters (ADCs) are their sampling rate and dynamic range. Power consumption and cost of an ADC are directly proportional to the sampling rate; hence, it is desirable to keep it as low as possible. The dynamic range of an ADC also plays an important role, and ideally, it should be greater than the signal's; otherwise, the signal will be clipped. To avoid clipping, modulo folding can be used before sampling, followed by an unfolding algorithm to recover the true signal. In this paper, we present a modulo hardware prototype that can be used before sampling to avoid clipping. Our modulo hardware operates prior to the sampling mechanism and can fold higher frequency signals compared to existing hardware. We present a detailed design of the hardware and also address key issues that arise during implementation. In terms of applications, we show the reconstruction of finite-rate-of-innovation signals which are beyond the dynamic range of the ADC. Our system operates at six times below the Nyquist rate of the signal and can accommodate eight-times larger signals than the ADC's dynamic range.

Hardware Implementation of Task-based Quantization in Multi-user Signal Recovery

Jan 27, 2023Abstract:Quantization plays a critical role in digital signal processing systems, allowing the representation of continuous amplitude signals with a finite number of bits. However, accurately representing signals requires a large number of quantization bits, which causes severe cost, power consumption, and memory burden. A promising way to address this issue is task-based quantization. By exploiting the task information for the overall system design, task-based quantization can achieve satisfying performance with low quantization costs. In this work, we apply task-based quantization to multi-user signal recovery and present a hardware prototype implementation. The prototype consists of a tailored configurable combining board, and a software-based processing and demonstration system. Through experiments, we verify that with proper design, the task-based quantization achieves a reduction of 25 fold in memory by reducing from 16 receivers with 16 bits each to 2 receivers with 5 bits each, without compromising signal recovery performance.

Hardware Prototype of a Time-Encoding Sub-Nyquist ADC

Jan 05, 2023Abstract:Analog-to-digital converters (ADCs) are key components of digital signal processing. Classical samplers in this framework are controlled by a global clock. At high sampling rates, clocks are expensive and power-hungry, thus increasing the cost and energy consumption of ADCs. It is, therefore, desirable to sample using a clock-less ADC at the lowest possible rate. An integrate-and-fire time-encoding machine (IF-TEM) is a time-based power-efficient asynchronous design that is not synced to a global clock. Finite-rate-of-innovation (FRI) signals, ubiquitous in various applications, have fewer degrees of freedom than the signal's Nyquist rate, enabling sub-Nyquist sampling signal models. This work proposes a power-efficient IF-TEM ADC architecture and demonstrates sub-Nyquist sampling and FRI signal recovery. Using an IF-TEM, we implement in hardware the first sub-Nyquist time-based sampler. We offer a feasible approach for accurately estimating the FRI parameters from IF-TEM data. The suggested hardware and reconstruction approach retrieves FRI parameters with an error of up to -25dB while operating at rates approximately 10 times lower than the Nyquist rate, paving the way to low-power ADC architectures.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge