Seyed Hadi Mirfarshbafan

Beamspace Equalization for mmWave Massive MIMO: Algorithms and VLSI Implementations

Nov 13, 2025

Abstract:Massive multiuser multiple-input multiple-output (MIMO) and millimeter-wave (mmWave) communication are key physical layer technologies in future wireless systems. Their deployment, however, is expected to incur excessive baseband processing hardware cost and power consumption. Beamspace processing leverages the channel sparsity at mmWave frequencies to reduce baseband processing complexity. In this paper, we review existing beamspace data detection algorithms and propose new algorithms as well as corresponding VLSI architectures that reduce data detection power. We present VLSI implementation results for the proposed architectures in a 22nm FDSOI process. Our results demonstrate that a fully-parallelized implementation of the proposed complex sparsity-adaptive equalizer (CSPADE) achieves up to 54% power savings compared to antenna-domain equalization. Furthermore, our fully-parallelized designs achieve the highest reported throughput among existing massive MIMO data detectors, while achieving better energy and area efficiency. We also present a sequential multiply-accumulate (MAC)-based architecture for CSPADE, which enables even higher power savings, i.e., up to 66%, compared to a MAC-based antenna-domain equalizer.

A Deep-Unfolding-Optimized Coordinate-Descent Data-Detector ASIC for mmWave Massive MIMO

Jan 24, 2025Abstract:We present a 22 nm FD-SOI (fully depleted silicon-on-insulator) application-specific integrated circuit (ASIC) implementation of a novel soft-output Gram-domain block coordinate descent (GBCD) data detector for massive multi-user (MU) multiple-input multiple-output (MIMO) systems. The ASIC simultaneously addresses the high throughput requirements for millimeter wave (mmWave) communication, stringent area and power budget per subcarrier in an orthogonal frequency-division multiplexing (OFDM) system, and error-rate performance challenges posed by realistic mmWave channels. The proposed GBCD algorithm utilizes a posterior mean estimate (PME) denoiser and is optimized using deep unfolding, which results in superior error-rate performance even in scenarios with highly correlated channels or where the number of user equipment (UE) data streams is comparable to the number of basestation (BS) antennas. The fabricated GBCD ASIC supports up to 16 UEs transmitting QPSK to 256-QAM symbols to a 128-antenna BS, and achieves a peak throughput of 7.1 Gbps at 367 mW. The core area is only 0.97 mm$^2$ thanks to a reconfigurable array of processing elements that enables extensive resource sharing. Measurement results demonstrate that the proposed GBCD data-detector ASIC achieves best-in-class throughput and area efficiency.

Hardware-Aware Beamspace Precoding for All-Digital mmWave Massive MU-MIMO

Aug 13, 2021

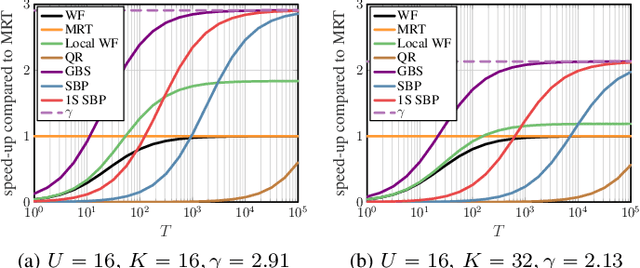

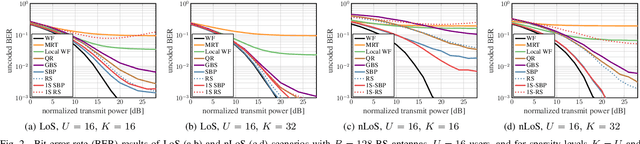

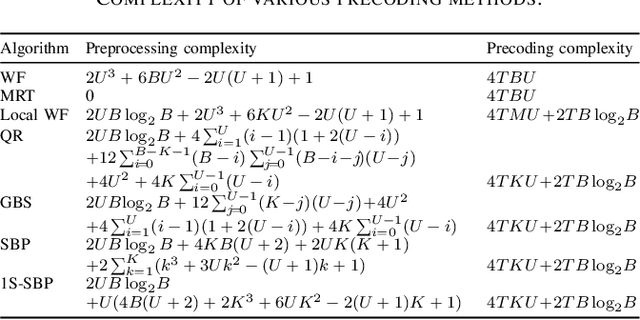

Abstract:Massive multi-user multiple-input multiple-output (MU-MIMO) wireless systems operating at millimeter-wave (mmWave) frequencies enable simultaneous wideband data transmission to a large number of users. In order to reduce the complexity of MU precoding in all-digital basestation architectures, we propose a two-stage precoding architecture that first performs precoding using a sparse matrix in the beamspace domain, followed by an inverse fast Fourier transform that converts the result to the antenna domain. The sparse precoding matrix requires a small number of multipliers and enables regular hardware architectures, which allows the design of hardware-efficient all-digital precoders. Simulation results demonstrate that our methods approach the error-rate of conventional Wiener filter precoding with more than 2x reduced complexity.

A Resolution-Adaptive 8 mm$^\text{2}$ 9.98 Gb/s 39.7 pJ/b 32-Antenna All-Digital Spatial Equalizer for mmWave Massive MU-MIMO in 65nm CMOS

Jul 23, 2021

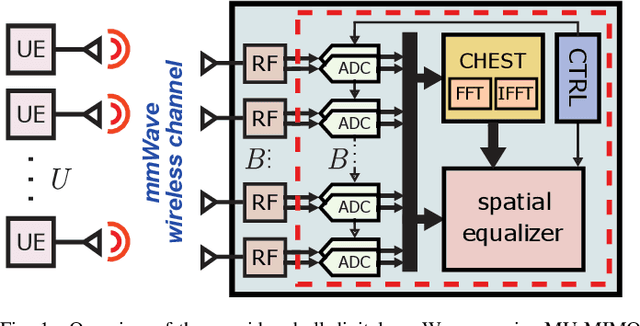

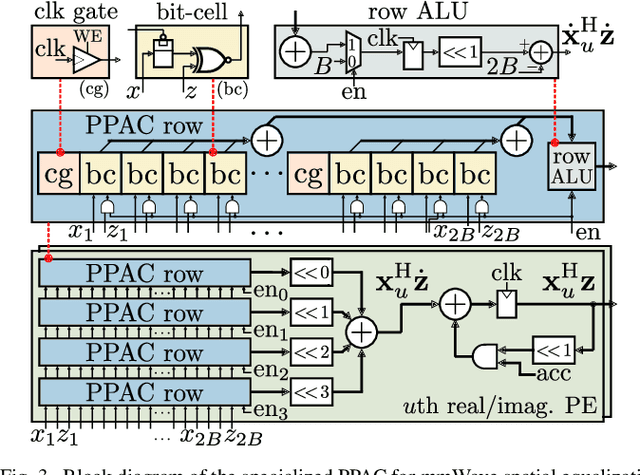

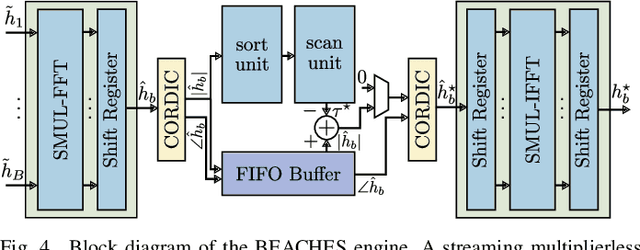

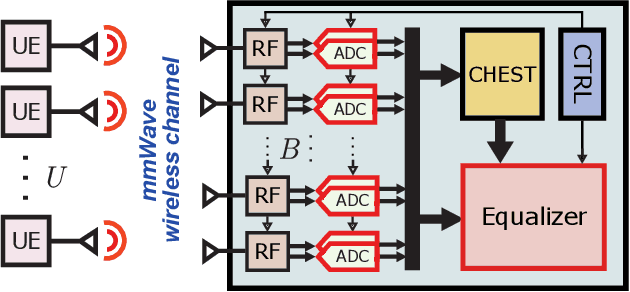

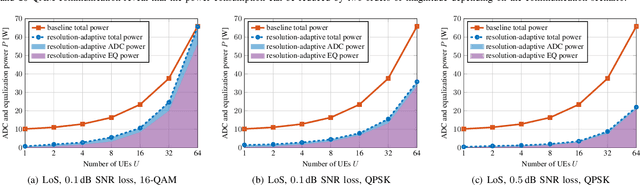

Abstract:All-digital millimeter-wave (mmWave) massive multi-user multiple-input multiple-output (MU-MIMO) receivers enable extreme data rates but require high power consumption. In order to reduce power consumption, this paper presents the first resolution-adaptive all-digital receiver ASIC that is able to adjust the resolution of the data-converters and baseband-processing engine to the instantaneous communication scenario. The scalable 32-antenna, 65 nm CMOS receiver occupies a total area of 8 mm$^\text{2}$ and integrates analog-to-digital converters (ADCs) with programmable gain and resolution, beamspace channel estimation, and a resolution-adaptive processing-in-memory spatial equalizer. With 6-bit ADC samples and a 4-bit spatial equalizer, our ASIC achieves a throughput of 9.98 Gb/s while being at least 2x more energy-efficient than state-of-the-art designs.

Resolution-Adaptive All-Digital Spatial Equalization for mmWave Massive MU-MIMO

Jul 23, 2021

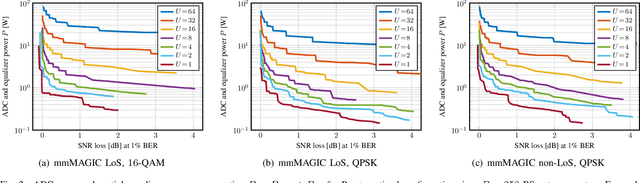

Abstract:All-digital basestation (BS) architectures for millimeter-wave (mmWave) massive multi-user multiple-input multiple-output (MU-MIMO), which equip each radio-frequency chain with dedicated data converters, have advantages in spectral efficiency, flexibility, and baseband-processing simplicity over hybrid analog-digital solutions. For all-digital architectures to be competitive with hybrid solutions in terms of power consumption, novel signal-processing methods and baseband architectures are necessary. In this paper, we demonstrate that adapting the resolution of the analog-to-digital converters (ADCs) and spatial equalizer of an all-digital system to the communication scenario (e.g., the number of users, modulation scheme, and propagation conditions) enables orders-of-magnitude power savings for realistic mmWave channels. For example, for a 256-BS-antenna 16-user system supporting 1 GHz bandwidth, a traditional baseline architecture designed for a 64-user worst-case scenario would consume 23 W in 28 nm CMOS for the ADC array and the spatial equalizer, whereas a resolution-adaptive architecture is able to reduce the power consumption by 6.7x.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge