Carsten Andrich

Background Subtraction with Drift Correction for Bistatic Radar Reflectivity Measurements

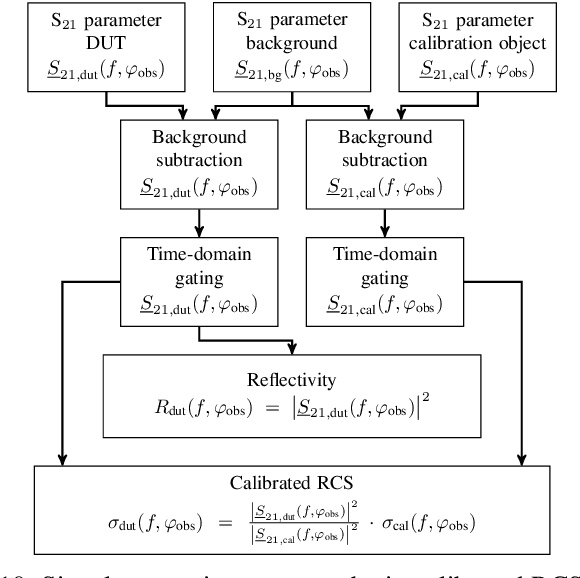

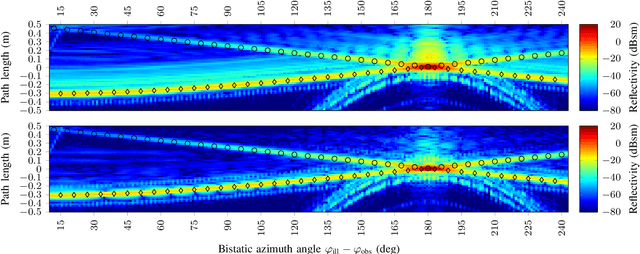

Jan 20, 2026Abstract:Fundamental research on bistatic radar reflectivity is highly relevant, e.g., to the upcoming mobile communication standard 6G, which includes integrated sensing and communication (ISAC). We introduce a model for correcting instrumentation drift during bistatic radar measurements in anechoic chambers. Usually, background subtraction is applied with the goal to yield the target reflection signal as best as possible while coherently subtracting all signals which were present in both the foreground and background measurement. However, even slight incoherences between the foreground and background measurement process deteriorate the result. We analyze these effects in real measurements in the frequency range 2-18 GHz, taken with the Bistatic Radar (BIRA) measurement facility at TU Ilmenau. Applying our proposed drift correction model, we demonstrate up to 40 dB improvement for the removal of direct line-of-sight antenna crosstalk over the state of the art.

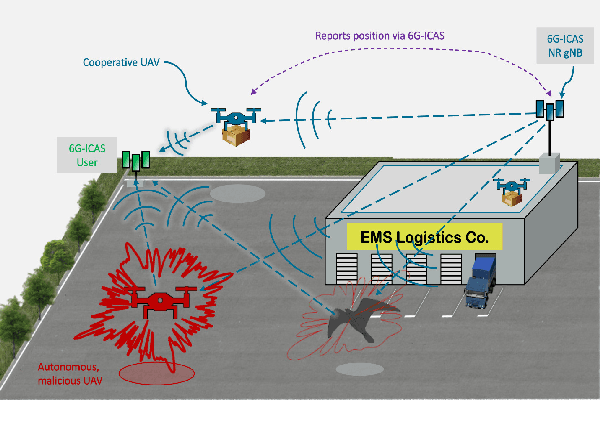

Enhancing Situational Awareness in ISAC Networks via Drone Swarms: A Real-World Channel Sounding Data Set

Jul 16, 2025Abstract:With the upcoming capabilities of integrated sensing and communication (ISAC) and the incorporation of user equipment (UE) like unmanned aerial vehicles (UAVs) in 6G mobile networks, there is a significant opportunity to enhance situational awareness through multi-static radar sensing in meshed ISAC networks. This paper presents a real-world channel sounding data set acquired using a testbed with synchronized, distributed ground-based sensor nodes and flying sensor nodes within a swarm of up to four drones. The conducted measurement campaign is designed to sense the bi-static reflectivity of objects such as parking cars, vertical take-off and landing (VTOL) aircraft, and small drones in multi-path environments. We detail the rationale behind the selection of the included scenarios and the configuration of the participating nodesand present exemplary results to demonstrate the potential of using collaborating drone swarms for multi-static radar tracking and localization in air-to-air (A2A) and air-to-ground (A2G) scenarios. The data sets are publicly available to support the development and validation of future ISAC algorithms in real-world environments rather than relying solely on simulation.

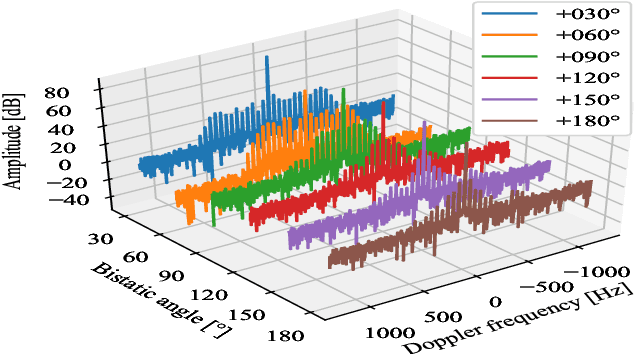

Modeling Micro-Doppler Signature of Multi-Propeller Drones in Distributed ISAC

Apr 07, 2025Abstract:Integrated Sensing and Communication (ISAC) will be one key feature of future 6G networks, enabling simultaneous communication and radar sensing. The radar sensing geometry of ISAC will be multistatic since that corresponds to the common distributed structure of a mobile communication network. Within this framework, micro-Doppler analysis plays a vital role in classifying targets based on their micromotions, such as rotating propellers, vibration, or moving limbs. However, research on bistatic micro-Doppler effects, particularly in ISAC systems utilizing OFDM waveforms, remains limited. Existing methods, including electromagnetic simulations often lack scalability for generating the large datasets required to train machine learning algorithms. To address this gap, this work introduces an OFDM-based bistatic micro-Doppler model for multi-propeller drones. The proposed model adapts the classic thin-wire model to include bistatic sensing configuration with an OFDM-like signal. Then, it extends further by incorporating multiple propellers and integrating the reflectivity of the drone's static parts. Measurements were performed to collect ground truth data for verification of the proposed model. Validation results show that the model generates micro-Doppler signatures closely resembling those obtained from measurements, demonstrating its potential as a tool for data generation. In addition, it offers a comprehensive approach to analyzing bistatic micro-Doppler effects.

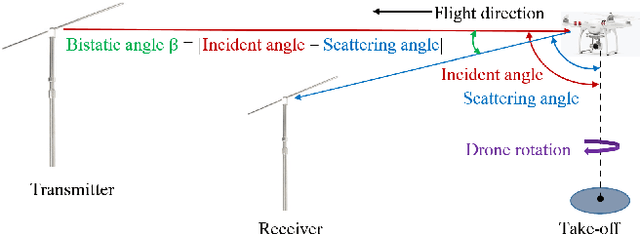

Bistatic Micro-Doppler Analysis of a Vertical Takeoff and Landing (VTOL) Drone in ICAS Framework

Feb 12, 2025Abstract:Integrated Communication and Sensing (ICAS) is a key technology that enables sensing functionalities within the next-generation mobile communication (6G). Joint design and optimization of both functionalities could allow coexistence, therefore it advances toward joint signal processing and using the same hardware platform and common spectrum. Contributing to ICAS sensing, this paper presents the measurement and analysis of the micro-Doppler signature of Vertical Takeoff and Landing (VTOL) drones. Measurement is performed with an OFDM-like communication signal and bistatic constellation, which is a typical case in ICAS scenarios. This work shows that micro-Doppler signatures can be used to precisely distinguish flight modes, such as take-off, landing, hovering, transition, and cruising.

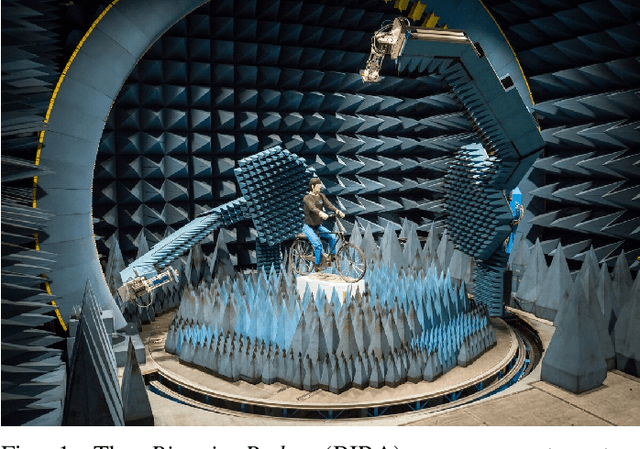

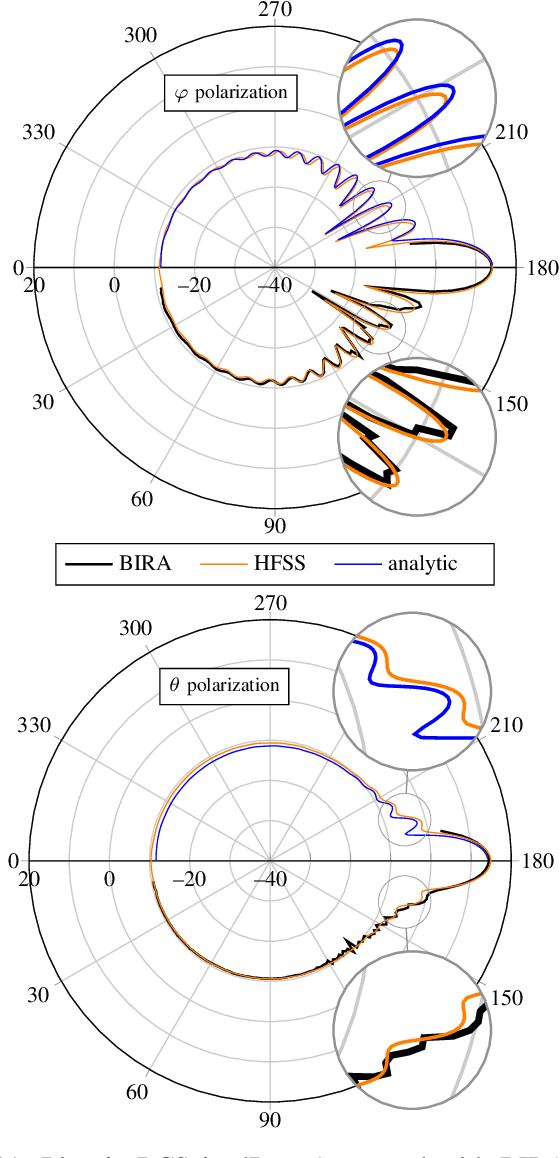

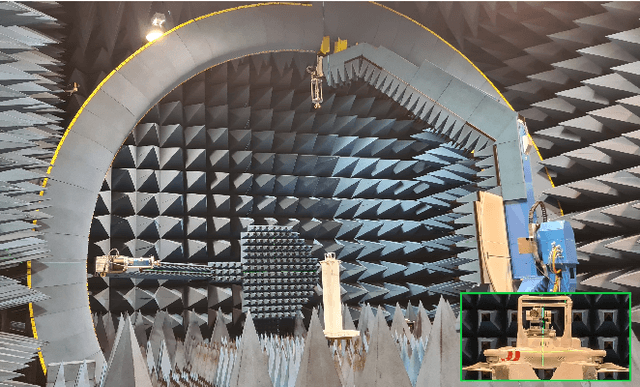

BIRA: A Spherical Bistatic Reflectivity Measurement System

Jul 18, 2024

Abstract:The upcoming 6G mobile communication standard will offer a revolutionary new feature: Integrated sensing and communication (ISAC) reuses mobile communication signals to realize multi-static radar for various applications including localization. Consequently, applied ISAC propagation research necessitates to evolve from classical monostatic radar cross section (RCS) measurement of static targets on to bistatic radar reflectivity characterization of dynamic objects. Here, we introduce our "Bistatic Radar" (BIRA) and antenna measurement facility for bistatic spherical positioning with sub-millimeter accuracy on a diameter of up to 7 m and with almost continuous frequency coverage from 0.7 up to 260 GHz. Currently, BIRA is the only bistatic measurement facility capable of unrestricted ISAC research: In addition to vector network analysis, BIRA employs advanced wideband transceiver technology with an instantaneous bandwidth of up to 4 GHz. These transceivers grant BIRA the unique ability to characterize dynamic targets in both Doppler and range, while also significantly accelerating RCS measurements of static objects.

Sounding-Based Evaluation of Multi-Sensor ISAC Networks for Drone Applications: Measurement and Simulation Perspectives

Feb 26, 2024

Abstract:With the upcoming multitude of commercial and public applications envisioned in the mobile 6G radio landscape using unmanned aerial vehicles (UAVs), integrated sensing and communication (ISAC) plays a key role to enable the detection and localization of passive objects with radar sensing, while optimizing the utilization of scarce resources. To explore the potential of future ISAC architectures with UAVs as mobile nodes in distributed multi-sensor networks, the system's fundamental capability to detect static and dynamic objects that reveal themselves by their bi-static back-scattering needs to be evaluated. Therefore, this paper addresses simulation- and measurement based data acquisition methods to gather knowledge about the bistatic reflectivity of single objects including their Micro-Doppler signature for object identification as well as the influence of multipath propagation in different environments on the localization accuracy and radar tracking performance. We show exemplary results from simulation models, bi-static reflectivity measurements in laboratory environment and real-flight channel sounding experiments in selected scenarios showcasing the potential of synthetic and measured data sets for development and evaluation of ISAC algorithms. The presented measurement data sets are publicly available to encourage the academic RF community to validate future algorithms using realistic scenarios alongside simulations models.

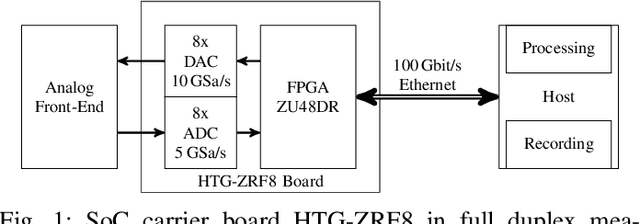

Accelerating Innovation in 6G Research: Real-Time Capable SDR System Architecture for Rapid Prototyping

Feb 22, 2024

Abstract:The next global mobile communication standard 6G strives to push the technological limits of radio frequency (RF) communication even further than its predecessors: Data rates beyond 100 Gbit/s, RF bandwidths above 1 GHz, and sub-millisecond latency necessitate very high performance development tools to enable the extent of innovation required for 6G's likely features. We propose a new SDR firmware and software architecture designed explicitly to meet these challenging requirements. It relies on Ethernet and commercial off-the-shelf network and server components to maximize flexibility and to reduce costs. We analyze state-of-the-art solutions (USRP X440 and other RFSoC-based systems), derive architectural design goals, explain resulting design decision in detail, and exemplify our architecture's implementation on the XCZU48DR RFSoC. Finally, we prove its performance via measurements and outline how the architecture surpasses the state-of-the-art with respect to sustained RF recording while maintaining high Ethernet bandwidth efficiency. Building a micro-Doppler radar example, we demonstrate its real-time and rapid application development capabilities.

Static Reflectivity and Micro-Doppler Signature of Drones for Distributed ICAS

Jan 25, 2024

Abstract:The integration of wireless communication and radar sensing is now getting a huge interest from researchers of two big societies, wireless communication and radar. The road map to the final goal and individual solutions to the challenges might differ in developing the Integrated Communication and Sensing (ICAS) system. However, the electromagnetic signature of the targets will be still valid for all variants of the ICAS system because the detection, localization and classification of the targets are involved. Therefore, this paper presents a study on static reflectivity and micro-Doppler signatures of drones together. To acquire the required data, the state-of-the-art measurement system, BiRa, is used.

Modelling Micro-Doppler Signature of Drone Propellers in Distributed ISAC

Jan 25, 2024

Abstract:Integrated Sensing and Communication (ISAC) comprises detection and analysis of non-cooperative targets by exploiting the resources of the mobile radio system. In this context, micro-Doppler is of great importance for target classification, in order to distinguish objects with local movements. For developing algorithms for target classification, it is necessary to have a large amount of target signatures. Aiming to generate these data, this paper proposes a mathematical model for the micro-Doppler of drone rotating propellers, and validate the proposed model by comparing it to measured micro-Doppler. Results show that the proposed mathematical model can generate micro-Doppler data very similar to those from measurement data.

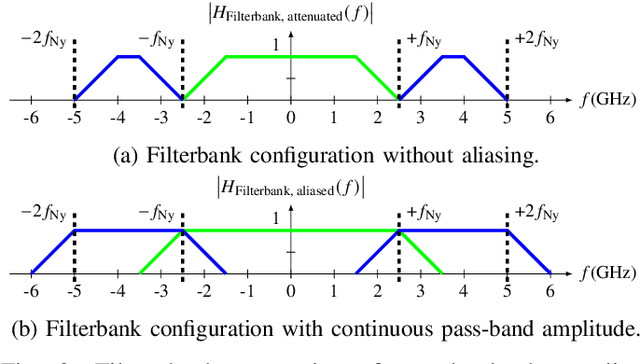

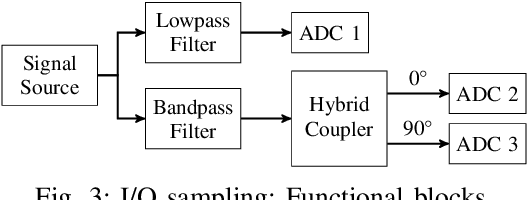

Receiver Bandwidth Extension Beyond Nyquist Using Channel Bonding

Oct 14, 2022

Abstract:Current and upcoming communication and sensing technologies require ever larger bandwidths. Channel bonding can be utilized to extend a receiver's instantaneous bandwidth beyond a single converter's Nyquist limit. Two potential joint front-end and converter design approaches are theoretically introduced, realized and evaluated in this paper. The Xilinx RFSoC platform with its 5 GSa/s analog to digital converters (ADCs) is used to implement both a hybrid coupler based in-phase/quadrature (I/Q) sampling and a time-interleaved sampling approach along with channel bonding. Both realizations are demonstrated to be able to reconstruct instantaneous bandwidths of 5 GHz with up to 49 dB image rejection ratio (IRR) typically within 4 to 8 dB the front-ends' theoretical limits.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge