Alexios Balatsoukas-Stimming

ComplexBeat: Breathing Rate Estimation from Complex CSI

Feb 18, 2025Abstract:In this paper, we explore the use of channel state information (CSI) from a WiFi system to estimate the breathing rate of a person in a room. In order to extract WiFi CSI components that are sensitive to breathing, we propose to consider the delay domain channel impulse response (CIR), while most state-of-the-art methods consider its frequency domain representation. One obstacle while processing the CSI data is that its amplitude and phase are highly distorted by measurement uncertainties. We thus also propose an amplitude calibration method and a phase offset calibration method for CSI measured in orthogonal frequency-division multiplexing (OFDM) multiple-input multiple-output (MIMO) systems. Finally, we implement a complete breathing rate estimation system in order to showcase the effectiveness of our proposed calibration and CSI extraction methods.

* This work has been accepted for publication in the 2021 IEEE Workshop on Signal Processing Systems (SiPS)

Training Channel Selection for Learning-based 1-bit Precoding in Massive MU-MIMO

Feb 17, 2025Abstract:Learning-based algorithms have gained great popularity in communications since they often outperform even carefully engineered solutions by learning from training samples. In this paper, we show that the selection of appropriate training examples can be important for the performance of such learning-based algorithms. In particular, we consider non-linear 1-bit precoding for massive multi-user MIMO systems using the C2PO algorithm. While previous works have already shown the advantages of learning critical coefficients of this algorithm, we demonstrate that straightforward selection of training samples that follow the channel model distribution does not necessarily lead to the best result. Instead, we provide a strategy to generate training data based on the specific properties of the algorithm, which significantly improves its error floor performance.

* This work is accepted by 2020 IEEE International Conference on Communications Workshops (ICC Workshops)

An SDR-Based Monostatic Wi-Fi System with Analog Self-Interference Cancellation for Sensing

Dec 11, 2024Abstract:Wireless sensing offers an alternative to wearables for contactless monitoring of human activity and vital signs. However, most existing systems use bistatic setups, which suffer from phase imperfections due to unsynchronized clocks. Monostatic systems overcome this issue, but are hindered by strong self-interference (SI) that require effective cancellation. We present a monostatic Wi-Fi sensing system that uses an auxiliary transmit RF chain to achieve SI cancellation levels of 40 dB, comparable to existing solutions with custom cancellation hardware. We demonstrate that the cancellation filter weights, fine-tuned using least-mean squares, can be directly repurposed for target sensing. Moreover, we achieve stable SI cancellation over 30 minutes in an office environment without fine-tuning, enabling traditional vital sign monitoring using channel estimates derived from baseband samples without the adaptation of the cancellation affecting the sensing channel -- a significant limitation in prior work. Experimental results confirm the detection of small, slow-moving targets, representative for breathing chest movements, at distances up to 10 meters in non-line-of-sight conditions.

Hardware Implementation of Projection-Aggregation Decoders for Reed-Muller Codes

Aug 20, 2024Abstract:This paper presents the hardware implementation of two variants of projection-aggregation-based decoding of Reed-Muller (RM) codes, namely unique projection aggregation (UPA) and collapsed projection aggregation (CPA). Our study focuses on introducing hardware architectures for both UPA and CPA. Through thorough analysis and experimentation, we observe that the hardware implementation of UPA exhibits superior resource usage and reduced energy consumption compared to CPA for the vanilla IPA decoder. This finding underscores a critical insight: software optimizations, in isolation, may not necessarily translate into hardware cost-effectiveness.

A Machine Learning Approach for Simultaneous Demapping of QAM and APSK Constellations

May 16, 2024

Abstract:As telecommunication systems evolve to meet increasing demands, integrating deep neural networks (DNNs) has shown promise in enhancing performance. However, the trade-off between accuracy and flexibility remains challenging when replacing traditional receivers with DNNs. This paper introduces a novel probabilistic framework that allows a single DNN demapper to demap multiple QAM and APSK constellations simultaneously. We also demonstrate that our framework allows exploiting hierarchical relationships in families of constellations. The consequence is that we need fewer neural network outputs to encode the same function without an increase in Bit Error Rate (BER). Our simulation results confirm that our approach approaches the optimal demodulation error bound under an Additive White Gaussian Noise (AWGN) channel for multiple constellations. Thereby, we address multiple important issues in making DNNs flexible enough for practical use as receivers.

A High-Performance and Low-Complexity 5G LDPC Decoder: Algorithm and Implementation

Oct 24, 2023Abstract:5G New Radio (NR) has stringent demands on both performance and complexity for the design of low-density parity-check (LDPC) decoding algorithms and corresponding VLSI implementations. Furthermore, decoders must fully support the wide range of all 5G NR blocklengths and code rates, which is a significant challenge. In this paper, we present a high-performance and low-complexity LDPC decoder, tailor-made to fulfill the 5G requirements. First, to close the gap between belief propagation (BP) decoding and its approximations in hardware, we propose an extension of adjusted min-sum decoding, called generalized adjusted min-sum (GA-MS) decoding. This decoding algorithm flexibly truncates the incoming messages at the check node level and carefully approximates the non-linear functions of BP decoding to balance the error-rate and hardware complexity. Numerical results demonstrate that the proposed fixed-point GAMS has only a minor gap of 0.1 dB compared to floating-point BP under various scenarios of 5G standard specifications. Secondly, we present a fully reconfigurable 5G NR LDPC decoder implementation based on GA-MS decoding. Given that memory occupies a substantial portion of the decoder area, we adopt multiple data compression and approximation techniques to reduce 42.2% of the memory overhead. The corresponding 28nm FD-SOI ASIC decoder has a core area of 1.823 mm2 and operates at 895 MHz. It is compatible with all 5G NR LDPC codes and achieves a peak throughput of 24.42 Gbps and a maximum area efficiency of 13.40 Gbps/mm2 at 4 decoding iterations.

Band-of-Interest-based Channel Impulse Response Fusion for Breathing Rate Estimation with UWB

Feb 06, 2023Abstract:The channel impulse response (CIR) obtained from the channel estimation step of various wireless systems is a widely used source of information in wireless sensing. Breathing rate is one of the important vital signs that can be retrieved from the CIR. Recently, there have been various works that extract the breathing rate from one carefully selected CIR delay bin that contains the breathing information. However, it has also been shown that the accuracy of this estimation is very sensitive to the measurement scenario, e.g., if there is any obstacle between the transceivers and the target, the position of the target, and the orientation of the target, since only one CIR delay bin does not contain a sufficient periodic component to retrieve the breathing rate. We focus on such scenarios and propose a CIR delay bin fusion method to merge several CIR bins to achieve a more accurate and reliable breathing rate estimate. We take measurements and showcase the advantages of the proposed method across scenarios.

Single-anchor UWB Localization using Channel Impulse Response Distributions

Nov 08, 2022Abstract:Ultra-wideband (UWB) devices are widely used in indoor localization scenarios. Single-anchor UWB localization shows advantages because of its simple system setup compared to conventional two-way ranging (TWR) and trilateration localization methods. In this work, we focus on single-anchor UWB localization methods that learn statistical features of the channel impulse response (CIR) in different location areas using a Gaussian mixture model (GMM). We show that by learning the joint distributions of the amplitudes of different delay components, we achieve a more accurate location estimate compared to considering each delay bin independently. Moreover, we develop a similarity metric between sets of CIRs. With this set-based similarity metric, we can further improve the estimation performance, compared to treating each snapshot separately. We showcase the advantages of the proposed methods in multiple application scenarios.

Recursive/Iterative unique Projection-Aggregation of RM codes

Oct 28, 2022Abstract:We describe recursive unique projection-aggregation (RUPA) decoding and iterative unique projection-aggregation (IUPA) decoding of Reed-Muller (RM) codes, which remove non-unique projections from the recursive projection-aggregation (RPA) and iterative projection-aggregation (IPA) algorithms respectively. We show that these algorithms have competitive error-correcting performance while requiring up to 95% projections less than the baseline RPA algorithm.

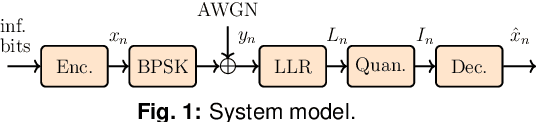

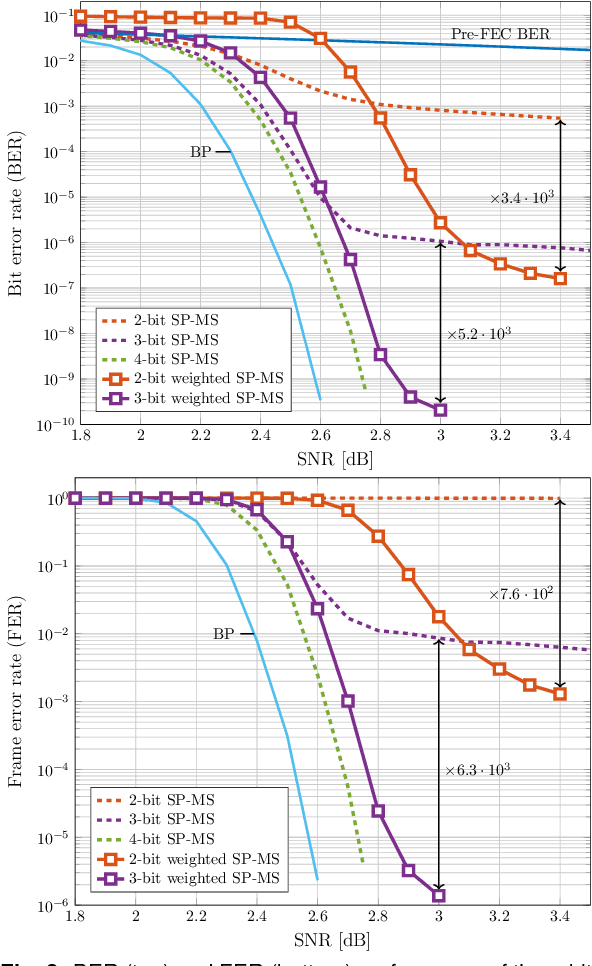

Reducing the Error Floor of the Sign-Preserving Min-Sum LDPC Decoder via Message Weighting of Low-Degree Variable Nodes

Jun 23, 2022

Abstract:Some low-complexity LDPC decoders suffer from error floors. We apply iteration-dependent weights to the degree-3 variable nodes to solve this problem. When the 802.3ca EPON LDPC code is considered, an error floor decrease of more than 3 orders of magnitude is achieved.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge