Xuyang Lu

A Semiparametric Bayesian Method for Instrumental Variable Analysis with Partly Interval-Censored Time-to-Event Outcome

Jan 23, 2025

Abstract:This paper develops a semiparametric Bayesian instrumental variable analysis method for estimating the causal effect of an endogenous variable when dealing with unobserved confounders and measurement errors with partly interval-censored time-to-event data, where event times are observed exactly for some subjects but left-censored, right-censored, or interval-censored for others. Our method is based on a two-stage Dirichlet process mixture instrumental variable (DPMIV) model which simultaneously models the first-stage random error term for the exposure variable and the second-stage random error term for the time-to-event outcome using a bivariate Gaussian mixture of the Dirichlet process (DPM) model. The DPM model can be broadly understood as a mixture model with an unspecified number of Gaussian components, which relaxes the normal error assumptions and allows the number of mixture components to be determined by the data. We develop an MCMC algorithm for the DPMIV model tailored for partly interval-censored data and conduct extensive simulations to assess the performance of our DPMIV method in comparison with some competing methods. Our simulations revealed that our proposed method is robust under different error distributions and can have superior performance over its parametric counterpart under various scenarios. We further demonstrate the effectiveness of our approach on an UK Biobank data to investigate the causal effect of systolic blood pressure on time-to-development of cardiovascular disease from the onset of diabetes mellitus.

WASABI: Widely-Spaced Array and Beamforming Design for Terahertz Range-Angle Secure Communications

Jan 17, 2022

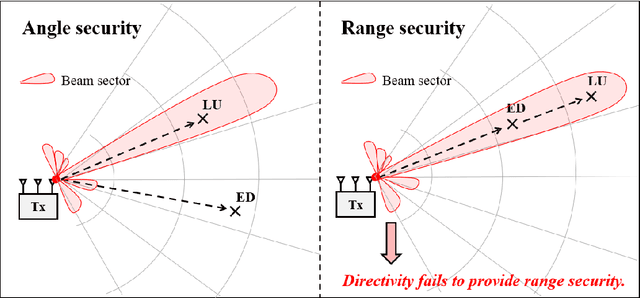

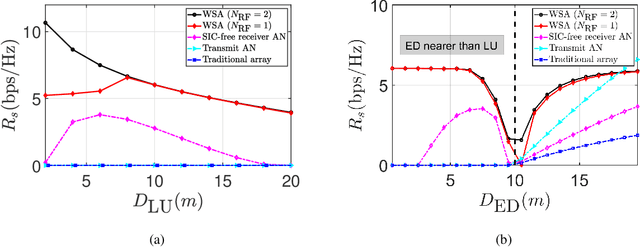

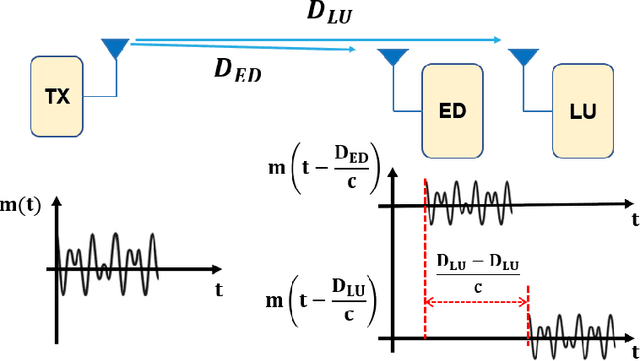

Abstract:Terahertz (THz) communications have naturally promising physical layer security (PLS) performance in the angular domain due to the high directivity feature. However, if eavesdroppers reside in the beam sector, the directivity fails to work effectively to handle this range-domain security problem. More critically, with an eavesdropper inside the beam sector and nearer to the transmitter than the legitimate receiver, i.e., in close proximity, secure communication is jeopardized. This open challenge motivates this work to study PLS techniques to enhance THz range-angle security. In this paper, a novel widely-spaced array and beamforming (WASABI) design for THz range-angle secure communication is proposed, based on the uniform planar array and hybrid beamforming. Specifically, the WASABI design is theoretically proved to achieve the optimal secrecy rate powered by the non-constrained optimum approaching (NCOA) algorithm with more than one RF chain, i.e., with the hybrid beamforming scheme. Moreover, with a low-complexity and sub-optimal analog beamforming, the WASABI scheme can achieve sub-optimal performance with less than 5% secrecy rate degradation. Simulation results illustrate that our proposed widely-spaced antenna communication scheme can ensure a 6bps/Hz secrecy rate when the transmit power is 10dBm. Finally, a frequency diverse array, as an advocated range security candidate in the literature, is proven to be ineffective to enhance range security.

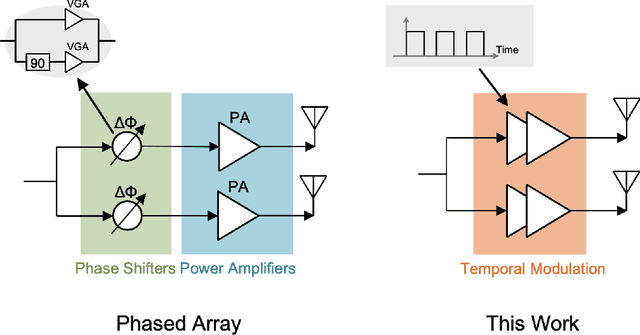

mmWave Spatial-Temporal Single Harmonic Switching Transmitter Arrays for High back-off Beamforming Efficiency

Jun 30, 2021

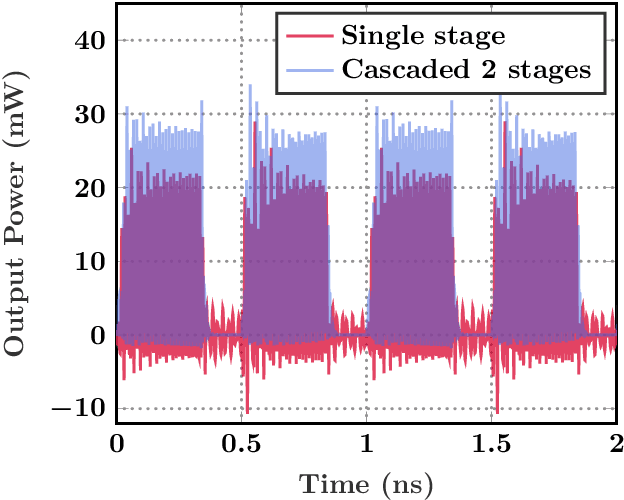

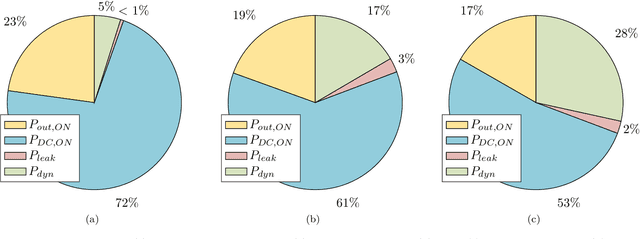

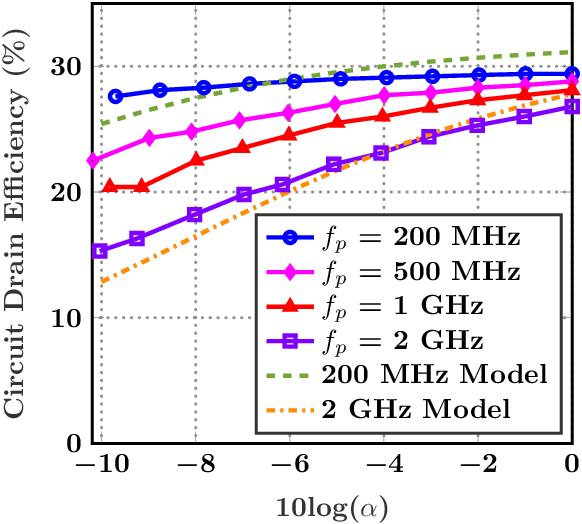

Abstract:This paper presents a spatial-temporal single harmonic switching (STHS) transmitter array architecture with enhanced efficiency in the power back-off (PBO) region. STHS is an electromagnetic and circuit co-designed and jointly optimized transmitter array that realizes beamforming and back-off power generation at the same time. The temporal dimension is originally added in STHS to achieve back-off efficiency enhancement, which can be combined with conventional power back-off enhancement methods such as Doherty amplifiers and envelope tracking. The design is validated through a simulation of a two-stage power amplifier in 65-nm CMOS at 77 GHz, which achieves a peak drain efficiency (DE) of 24.2%, a 22% DE at 3-dB PBO, 16% DE at 6-dB PBO, and 10.2% at 9-dB PBO. The efficiency exhibits a 57% improvement at 3-dB PBO, 100% improvement at 6-dB PBO, and 190% improvement at 9-dB PBO compared with class A/B amplifier.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge