Sudhakar Pamarti

Voltage-Controlled Magnetoelectric Devices for Neuromorphic Diffusion Process

Jul 17, 2024

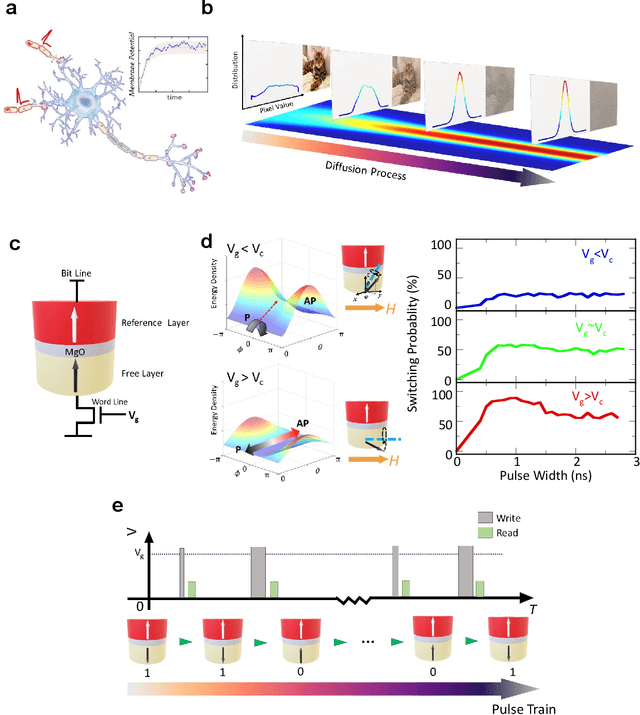

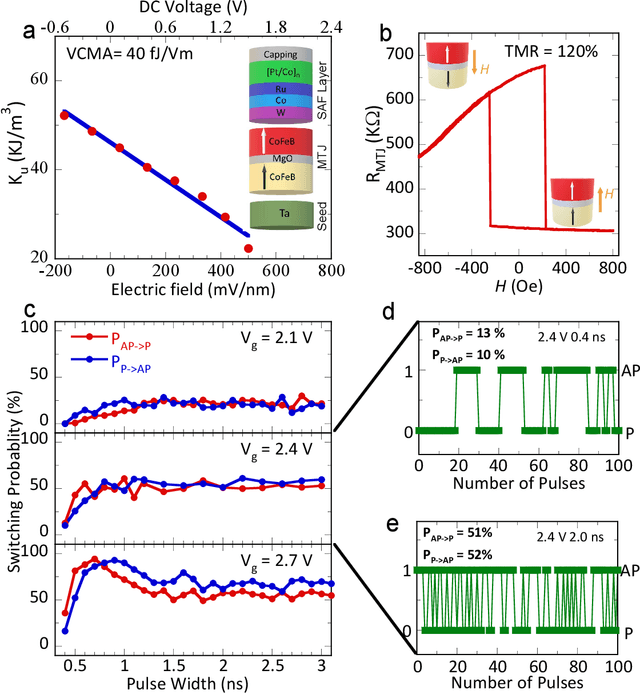

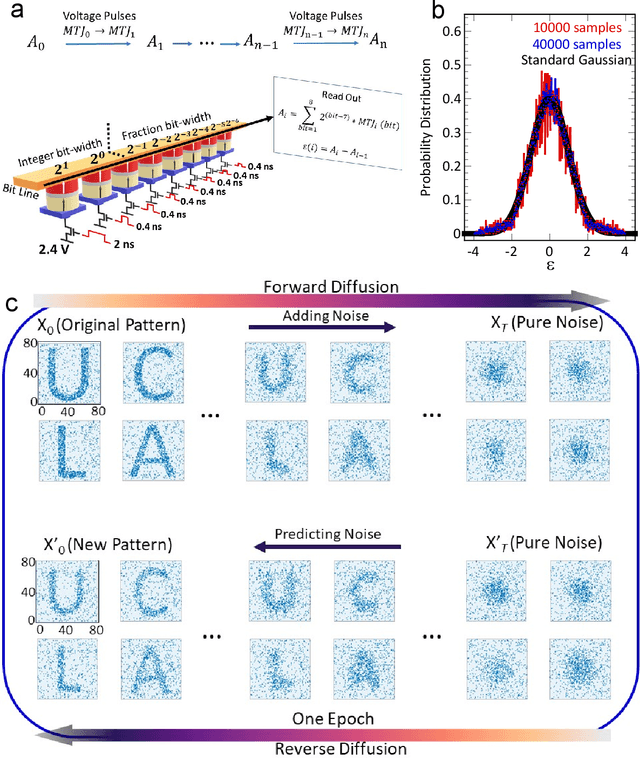

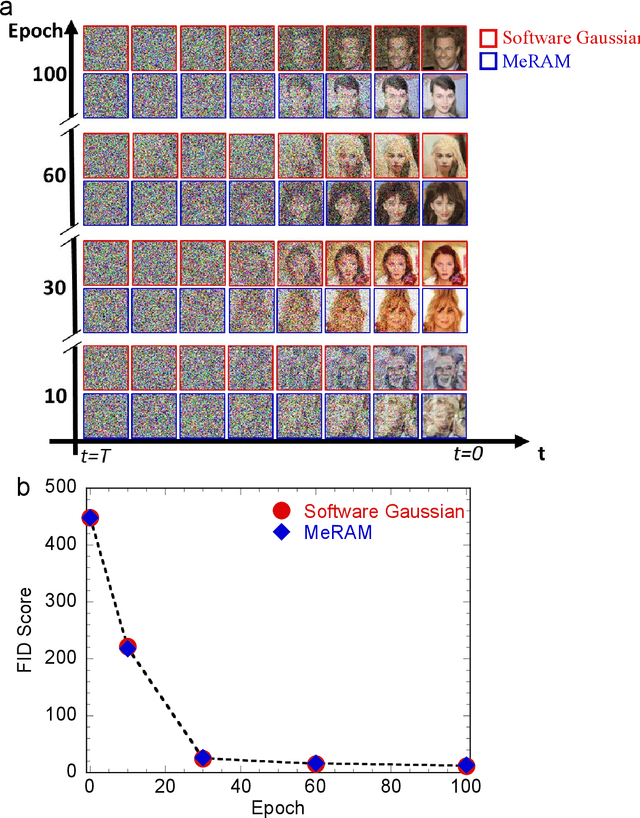

Abstract:Stochastic diffusion processes are pervasive in nature, from the seemingly erratic Brownian motion to the complex interactions of synaptically-coupled spiking neurons. Recently, drawing inspiration from Langevin dynamics, neuromorphic diffusion models were proposed and have become one of the major breakthroughs in the field of generative artificial intelligence. Unlike discriminative models that have been well developed to tackle classification or regression tasks, diffusion models as well as other generative models such as ChatGPT aim at creating content based upon contexts learned. However, the more complex algorithms of these models result in high computational costs using today's technologies, creating a bottleneck in their efficiency, and impeding further development. Here, we develop a spintronic voltage-controlled magnetoelectric memory hardware for the neuromorphic diffusion process. The in-memory computing capability of our spintronic devices goes beyond current Von Neumann architecture, where memory and computing units are separated. Together with the non-volatility of magnetic memory, we can achieve high-speed and low-cost computing, which is desirable for the increasing scale of generative models in the current era. We experimentally demonstrate that the hardware-based true random diffusion process can be implemented for image generation and achieve comparable image quality to software-based training as measured by the Frechet inception distance (FID) score, achieving ~10^3 better energy-per-bit-per-area over traditional hardware.

A Schottky-Diode-Based Wake-Up Receiver for IoT Applications

May 31, 2021

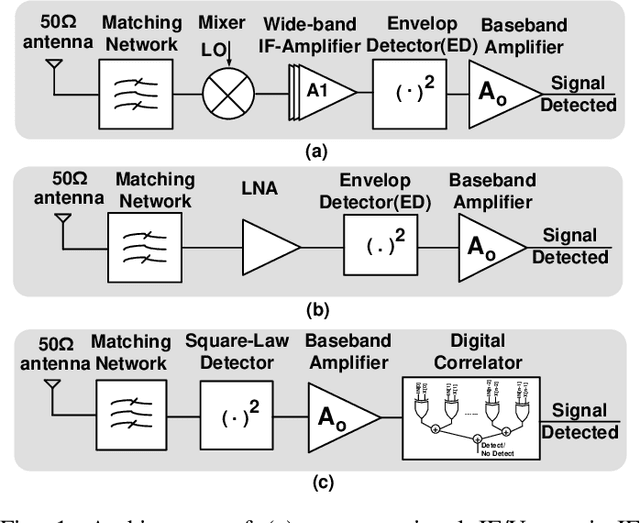

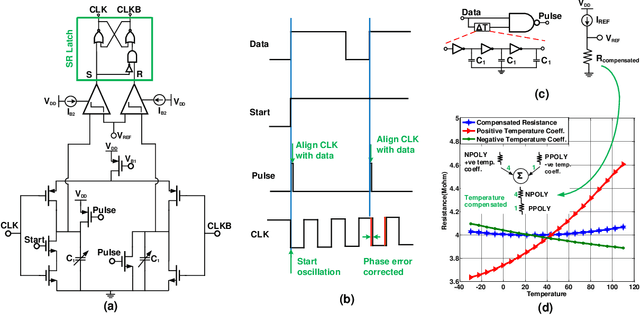

Abstract:This paper presents an always-on low-power wake-up receiver (WuRx) that activates the remainder of the system when a wake-up signal is detected. The proposed receiver has two phases of waking up. The first phase uses an integrated CMOS Schottky diodes to detect the signal power at a low bias current. The approach dissipates low quiescent power and allows the reuse of the design in multiple frequency bands with only modifying the matching network. In the second phase, a data-locked startable oscillator is proposed to correlate the received data with a target signature. This design eliminates the area and power dissipation of an external crystal oscillator and only turns on when the second phase is activated. By correlating to a target signature, the second phase also reduces the probability of a false alarm (PFA) that would otherwise wake up the high-power bulk of the system. The two-phase approach leads to significant reduction in average power consumption when compared to a single-phase design. This implementation targets sub-ms wake-up latency and operates in the unlicensed band at a 750-MHz carrier frequency with a data rate of 200 kbps. The design achieves $\sim$8.45pJ/bit and $<$-50 dBm of input sensitivity and average power of 1.69$\mu$W. The system is implemented in 65-nm CMOS technology and occupies an area of 1mm$\times$0.75mm.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge