Efficient Hardware Implementation of Incremental Learning and Inference on Chip

Paper and Code

Nov 18, 2019

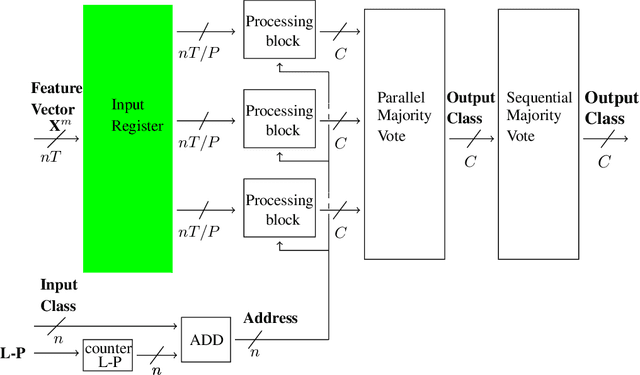

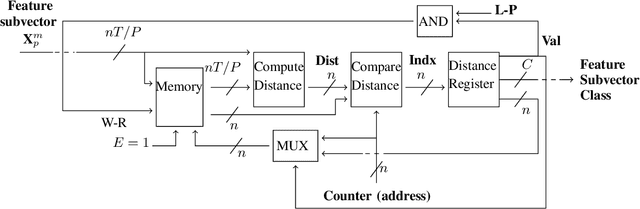

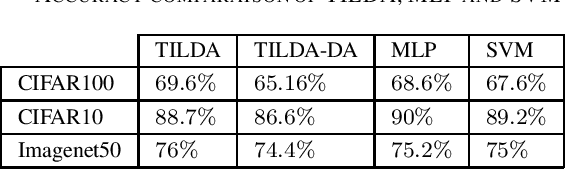

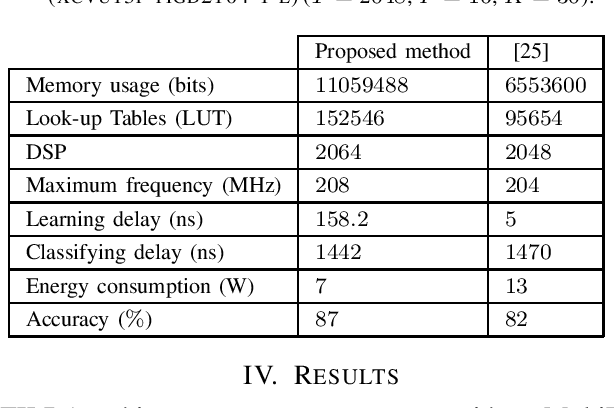

In this paper, we tackle the problem of incrementally learning a classifier, one example at a time, directly on chip. To this end, we propose an efficient hardware implementation of a recently introduced incremental learning procedure that achieves state-of-the-art performance by combining transfer learning with majority votes and quantization techniques. The proposed design is able to accommodate for both new examples and new classes directly on the chip. We detail the hardware implementation of the method (implemented on FPGA target) and show it requires limited resources while providing a significant acceleration compared to using a CPU.

* Boukli Hacene, G., Gripon, V., Farrugia, N., Arzel, M., &

Jezequel, M. (2019). Efficient Hardware Implementation of Incremental

Learning and Inference on Chip. In 2019 IEEE International NEWCAS Conference

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge