Timur Zirtiloglu

Power-Efficient Sampling

Dec 18, 2023

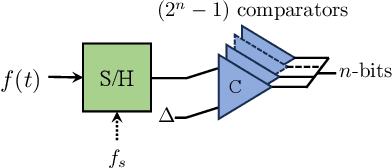

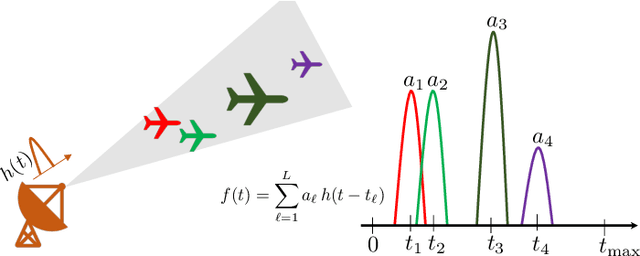

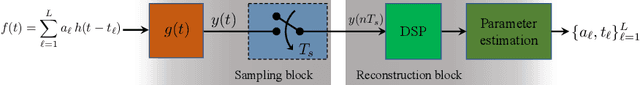

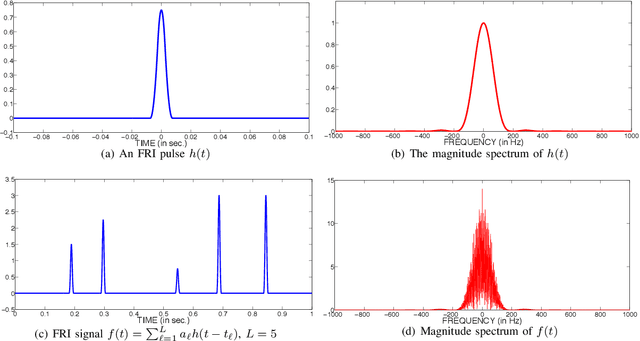

Abstract:Analog-to-digital converters (ADCs) facilitate the conversion of analog signals into a digital format. While the specific designs and settings of ADCs can vary depending on their applications, it is crucial in many modern applications to minimize their power consumption. The significance of low-power ADCs is particularly evident in fields like mobile and handheld devices reliant on battery operation. Key parameters of the ADCs that dictate the ADC's power are its sampling rate, dynamic range, and number of quantization bits. Typically, these parameters are required to be higher than a threshold value but can be reduced by using the structure of the signal and by leveraging preprocessing and the system application needs. In this review, we discuss four approaches relevant to a variety of applications.

Robust Task-Specific Beamforming with Low-Resolution ADCs for Power-Efficient Hybrid MIMO Receivers

Nov 30, 2022Abstract:Multiple-input multiple-output (MIMO) systems exploit spatial diversity to facilitate multi-user communications with high spectral efficiency by beamforming. As MIMO systems utilize multiple antennas and radio frequency (RF) chains, they are typically costly to implement and consume high power. A common method to reduce the cost of MIMO receivers is utilizing less RF chains than antennas by employing hybrid analog/digital beamforming (HBF). However, the added analog circuitry involves active components whose consumed power may surpass that saved in RF chain reduction. An additional method to realize power-efficient MIMO systems is to use low-resolution analog-to-digital converters (ADCs), which typically compromises signal recovery accuracy. In this work, we propose a power-efficient hybrid MIMO receiver with low-quantization rate ADCs, by jointly optimizing the analog and digital processing in a hardware-oriented manner using task-specific quantization techniques. To mitigate power consumption on the analog front-end, we utilize efficient analog hardware architecture comprised of sparse low-resolution vector modulators, while accounting for their properties in design to maintain recovery accuracy and mitigate interferers in congested environments. To account for common mismatches induced by non-ideal hardware and inaccurate channel state information, we propose a robust mismatch aware design. Supported by numerical simulations and power analysis, our power-efficient MIMO receiver achieves comparable signal recovery performance to power-hungry fully-digital MIMO receivers using high-resolution ADCs. Furthermore, our receiver outperforms the task-agnostic HBF receivers with low-rate ADCs in recovery accuracy at lower power and successfully copes with hardware mismatches.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge