Hamid Soleimani

Hardware realisation of nonlinear dynamical systems for and from biology

Aug 17, 2021

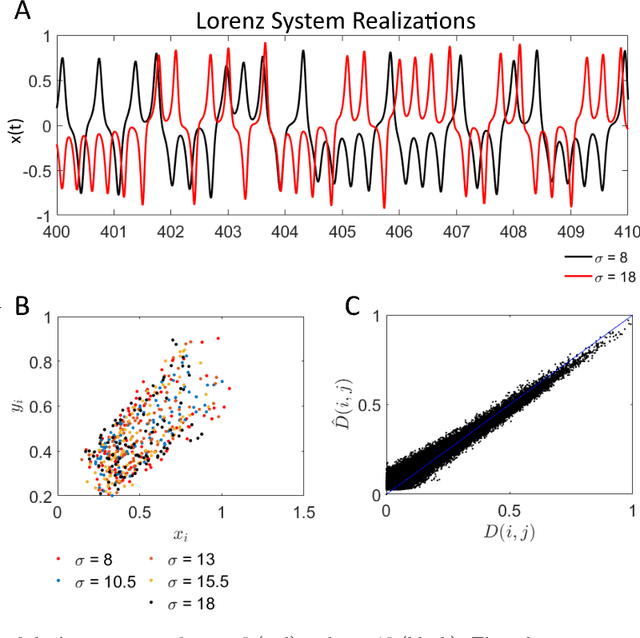

Abstract:The focus of this thesis is on the applications of nonlinear dynamical systems in bioengineering which are mainly used in large-scale and generally categorised into two groups: (1) dynamical systems from biology (2) dynamical systems for biology. The mathematical models describing the dynamical systems used in the above systems can be simulated with the use of powerful software such as MATLAB, however, for large-scale simulations software begins to collapse. Besides, computer-based simulations are not always suitable for interfacing with biological/physical systems where continuous monitoring with low power and area consumption might be required. To alleviate these issues, a few novel hardware techniques for both aforementioned groups are proposed and their hardware results compared and validated by software simulations.

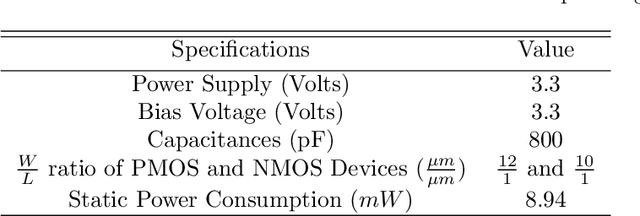

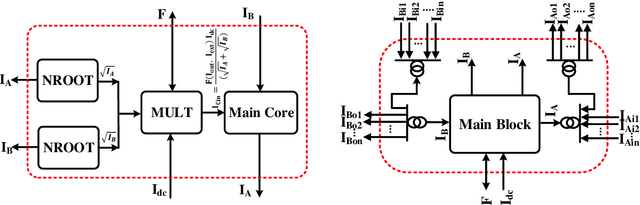

Neuromorphic Processing: A Unifying Tutorial

Aug 13, 2021

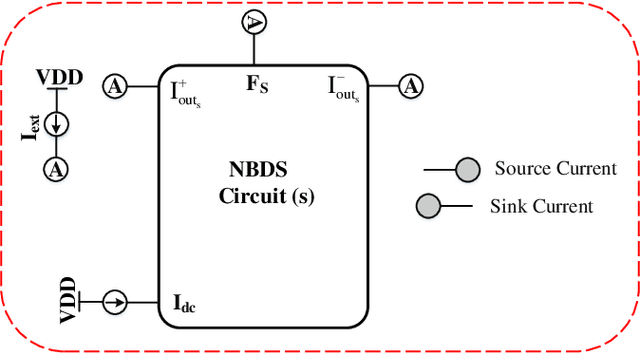

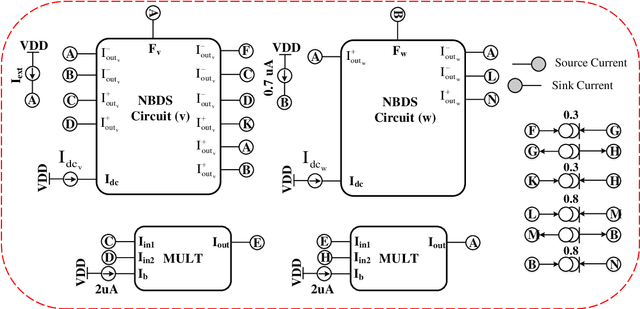

Abstract:All systolic or distributed neuromorphic architectures require power-efficient processing nodes. In this paper, a unifying tutorial is presented which implements multiple neuromorphic processing elements using a systematic analog approach including synapse, neuron and astrocyte models. It is shown that the proposed approach can successfully synthesize multidimensional dynamical systems into analog circuitry with minimum effort.

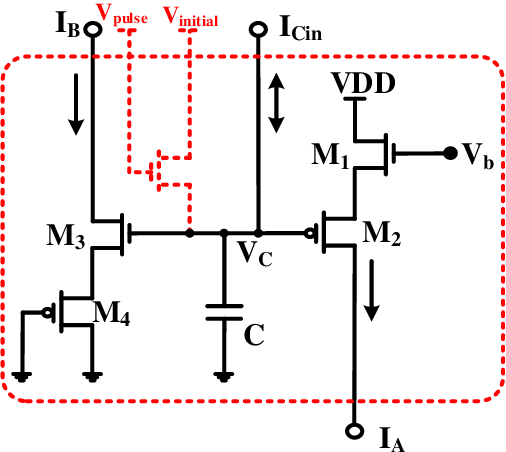

A Generalized Strong-Inversion CMOS Circuitry for Neuromorphic Applications

Jul 28, 2020

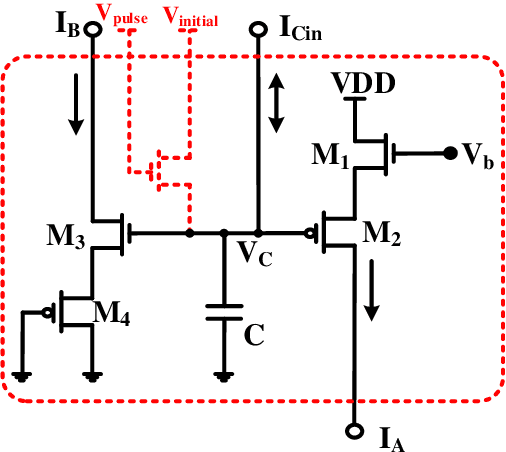

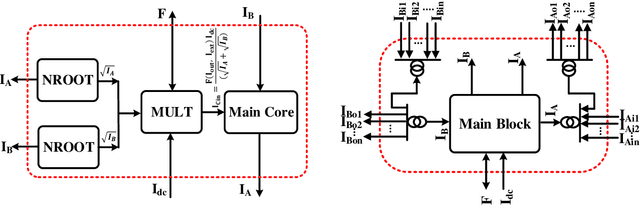

Abstract:It has always been a challenge in the neuromorphic field to systematically translate biological models into analog electronic circuitry. In this paper, a generalized circuit design platform is introduced where biological models can be conveniently implemented using CMOS circuitry operating in strong-inversion. The application of the method is demonstrated by synthesizing a relatively complex two-dimensional (2-D) nonlinear neuron model. The validity of our approach is verified by nominal simulated results with realistic process parameters from the commercially available AMS 0.35 um technology. The circuit simulation results exhibit regular spiking responses in good agreement with their mathematical counterpart.

A High GOPs/Slice Time Series Classifier for Portable and Embedded Biomedical Applications

Nov 01, 2018

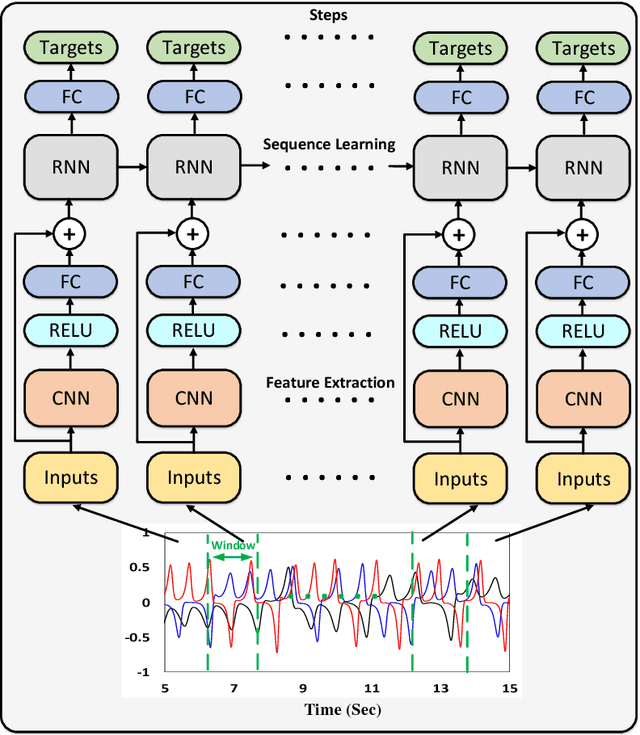

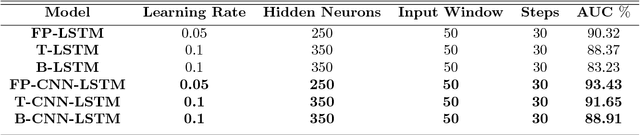

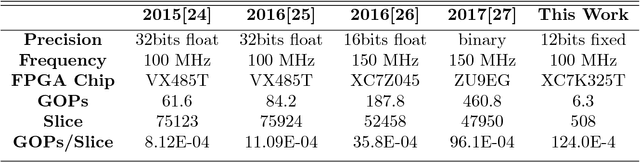

Abstract:Nowadays a diverse range of physiological data can be captured continuously for various applications in particular wellbeing and healthcare. Such data require efficient methods for classification and analysis. Deep learning algorithms have shown remarkable potential regarding such analyses, however, the use of these algorithms on low-power wearable devices is challenged by resource constraints such as area and power consumption. Most of the available on-chip deep learning processors contain complex and dense hardware architectures in order to achieve the highest possible throughput. Such a trend in hardware design may not be efficient in applications where on-node computation is required and the focus is more on the area and power efficiency as in the case of portable and embedded biomedical devices. This paper presents an efficient time-series classifier capable of automatically detecting effective features and classifying the input signals in real-time. In the proposed classifier, throughput is traded off with hardware complexity and cost using resource sharing techniques. A Convolutional Neural Network (CNN) is employed to extract input features and then a Long-Short-Term-Memory (LSTM) architecture with ternary weight precision classifies the input signals according to the extracted features. Hardware implementation on a Xilinx FPGA confirm that the proposed hardware can accurately classify multiple complex biomedical time series data with low area and power consumption and outperform all previously presented state-of-the-art records. Most notably, our classifier reaches 1.3$\times$ higher GOPs/Slice than similar state of the art FPGA-based accelerators.

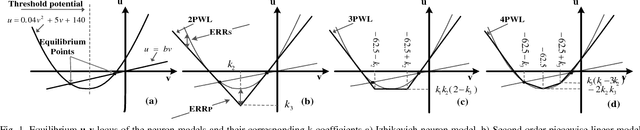

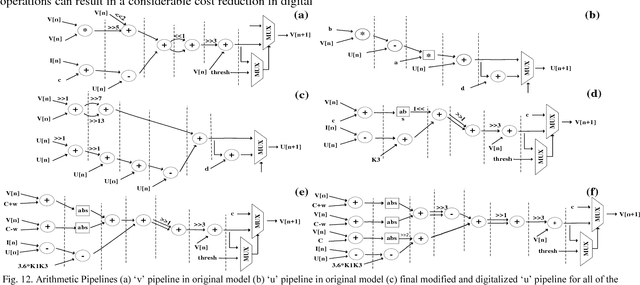

Biologically Inspired Spiking Neurons : Piecewise Linear Models and Digital Implementation

Dec 16, 2012

Abstract:There has been a strong push recently to examine biological scale simulations of neuromorphic algorithms to achieve stronger inference capabilities. This paper presents a set of piecewise linear spiking neuron models, which can reproduce different behaviors, similar to the biological neuron, both for a single neuron as well as a network of neurons. The proposed models are investigated, in terms of digital implementation feasibility and costs, targeting large scale hardware implementation. Hardware synthesis and physical implementations on FPGA show that the proposed models can produce precise neural behaviors with higher performance and considerably lower implementation costs compared with the original model. Accordingly, a compact structure of the models which can be trained with supervised and unsupervised learning algorithms has been developed. Using this structure and based on a spike rate coding, a character recognition case study has been implemented and tested.

* 14 pages, 16 figures

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge