Supported-BinaryNet: Bitcell Array-based Weight Supports for Dynamic Accuracy-Latency Trade-offs in SRAM-based Binarized Neural Network

Paper and Code

Nov 26, 2019

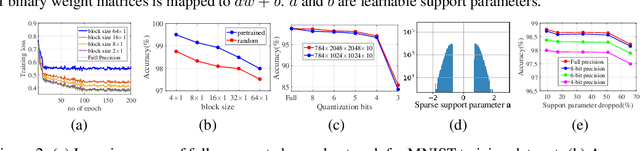

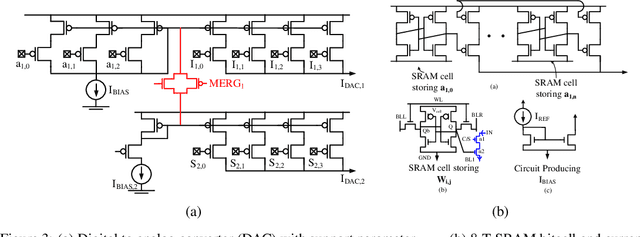

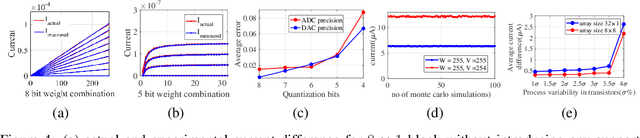

In this work, we introduce bitcell array-based support parameters to improve the prediction accuracy of SRAM-based binarized neural network (SRAM-BNN). Our approach enhances the training weight space of SRAM-BNN while requiring minimal overheads to a typical design. More flexibility of the weight space leads to higher prediction accuracy in our design. We adapt row digital-to-analog (DAC) converter, and computing flow in SRAM-BNN for bitcell array-based weight supports. Using the discussed interventions, our scheme also allows a dynamic trade-off of accuracy against latency to address dynamic latency constraints in typical real-time applications. We specifically discuss results on two training cases: (i) learning of support parameters on a pre-trained BNN and (ii) simultaneous learning of supports and weight binarization. In the former case, our approach reduces classification error in MNIST by 35.71% (error rate decreases from 1.4% to 0.91%). In the latter case, the error is reduced by 27.65% (error rate decreases from 1.4% to 1.13%). To reduce the power overheads, we propose a dynamic drop out a part of the support parameters. Our architecture can drop out 52% of the bitcell array-based support parameters without losing accuracy. We also characterize our design under varying degrees of process variability in the transistors.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge