Power Modeling in mm-Wave and Terahertz CMOS Transmitters for Wireless Network-on-Chip

Paper and Code

Oct 30, 2024

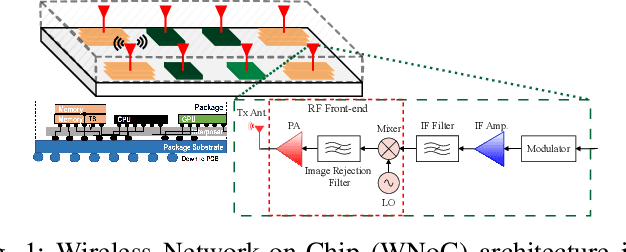

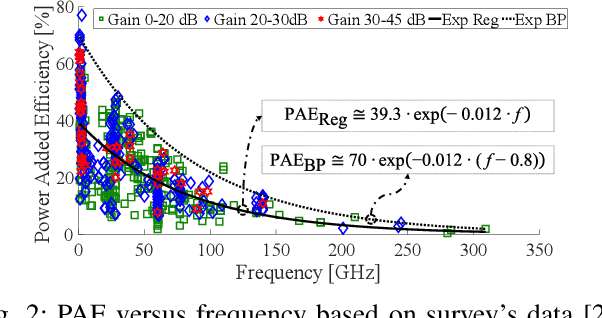

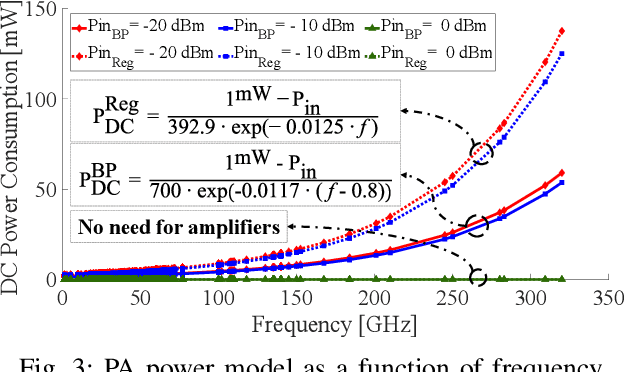

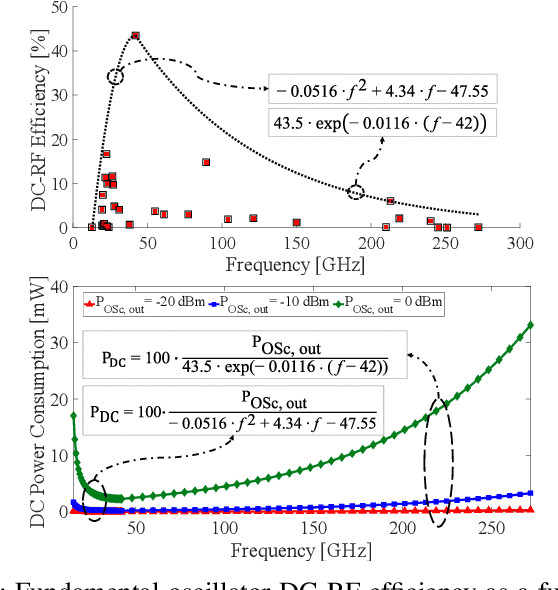

Wireless Network-on-Chip (WNoC) systems, which interconnect chips using wireless links, face significant challenges in area and power consumption. To tackle these constraints, behavioral models (BMs) are crucial for assessing system performance under various conditions and optimizing parameters like data throughput and power consumption. Building transceivers (TRXs) physically is costly and time-consuming, making modeling a more practical approach. This paper develops a power consumption model for the sub-blocks of a WNoC transmitter (TX) at the chip level. By integrating these BMs with MATLAB, we aim to create a power model for TXs in WNoC architectures, optimized for CMOS technology operating at millimeter-wave and terahertz frequencies.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge