Control Architecture of the Double-Cross-Correlation Processor for Sampling-Rate-Offset Estimation in Acoustic Sensor Networks

Paper and Code

May 28, 2021

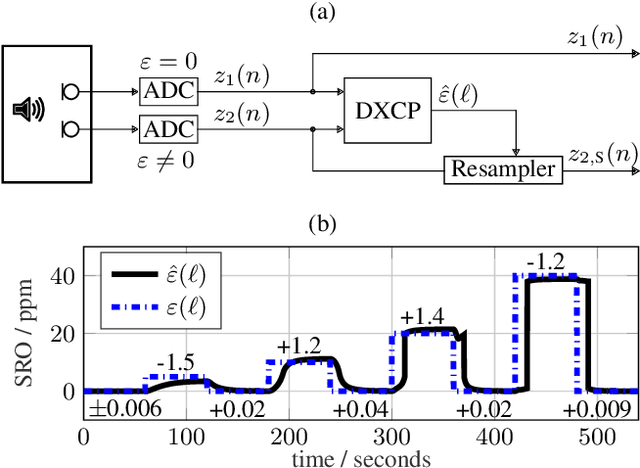

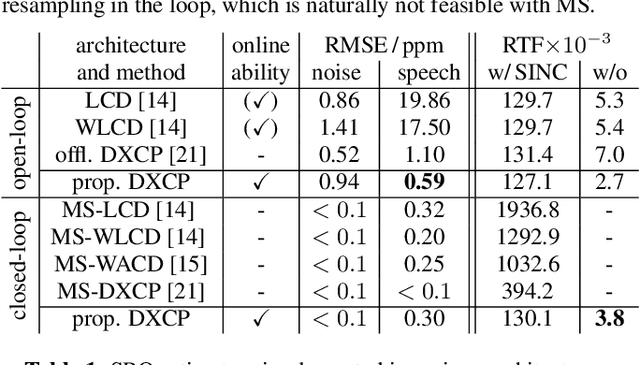

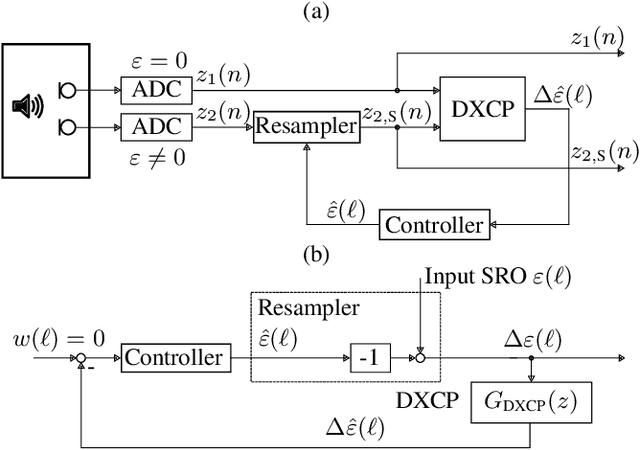

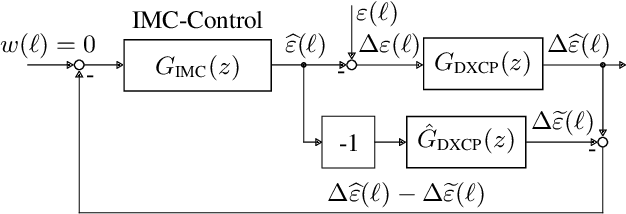

Distributed hardware of acoustic sensor networks bears inconsistency of local sampling frequencies, which is detrimental to signal processing. Fundamentally, sampling rate offset (SRO) nonlinearly relates the discrete-time signals acquired by different sensor nodes. As such, retrieval of SRO from the available signals requires nonlinear estimation, like double-cross-correlation processing (DXCP), and frequently results in biased estimation. SRO compensation by asynchronous sampling rate conversion (ASRC) on the signals then leaves an unacceptable residual. As a remedy to this problem, multi-stage procedures have been devised to diminish the SRO residual with multiple iterations of SRO estimation and ASRC over the entire signal. This paper converts the mechanism of offline multi-stage processing into a continuous feedback-control loop comprising a controlled ASRC unit followed by an online implementation of DXCP-based SRO estimation. To support the design of an optimum internal model control unit for this closed-loop system, the paper deploys an analytical dynamical model of the proposed online DXCP. The resulting control architecture then merely applies a single treatment of each signal frame, while efficiently diminishing SRO bias with time. Evaluations with both speech and Gaussian input demonstrate that the high accuracy of multi-stage processing is maintained at the low complexity of single-stage (open-loop) processing.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge