Sun Il Kwon

Cross-Detection and Dual-Side Monitoring Schemes for FPGA-Based High-Accuracy and High-Precision Time-to-Digital Converters

Oct 12, 2024

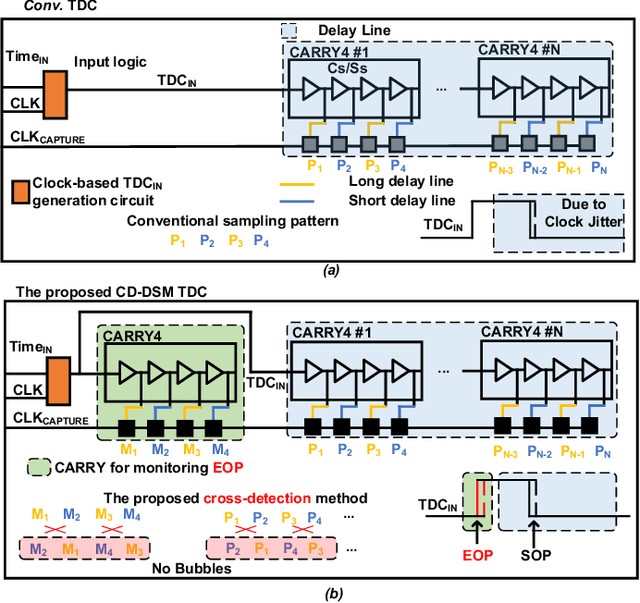

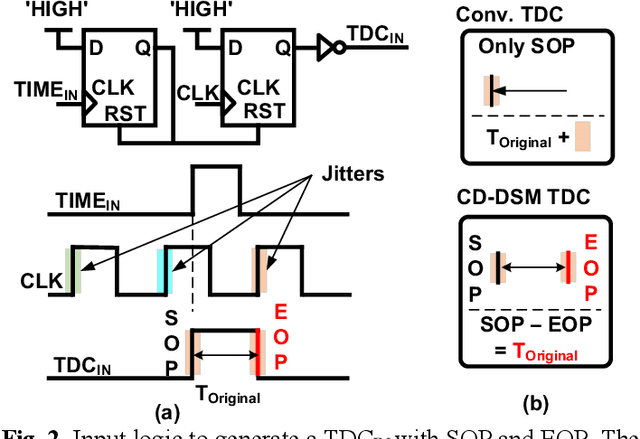

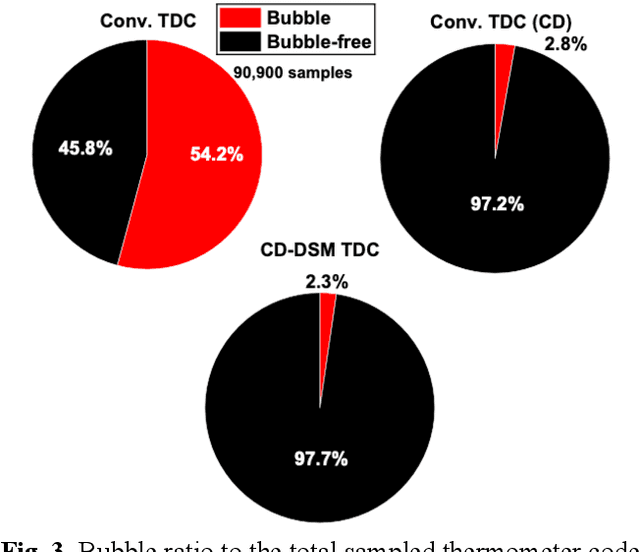

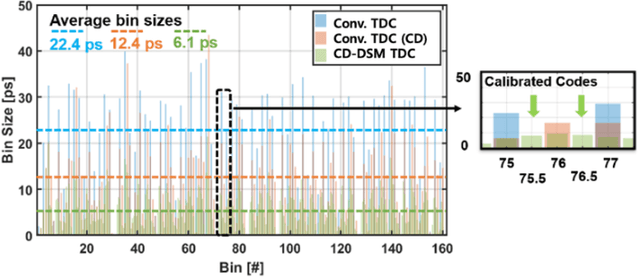

Abstract:This study presents a novel field-programmable gate array (FPGA)-based Time-to-Digital Converter (TDC) design suitable for high timing resolution applications, utilizing two new techniques. First, a cross-detection (CD) method is introduced that minimizes the occurrence of bubbles, which cause inaccuracy in the timing measurement of a TDC in thermometer codes, by altering the conventional sampling pattern, thereby yielding an average bin size half of its typical size. The second technique employs dual-side monitoring (DSM) of thermometer codes, including end-of-propagation (EOP) and start-of-propagation (SOP). Distinct from conventional TDCs, which focus solely on SOP thermometer codes, this technique utilizes EOP to calibrate SOP, simultaneously enhancing time resolution and the TDC's stability against changes in temperature and location. The proposed DSM scheme necessitates only an additional CARRY4 for capturing the EOP thermometer code, rendering it a resource-efficient solution. The CD-DSM TDC has been successfully implemented on a Virtex-7 Xilinx FPGA (a 28-nm process), with an average bin size of 6.1 ps and a root mean square of 3.8 ps. Compared to conventional TDCs, the CD-DSM TDC offers superior linearity. The successful measurement of ultra-high coincidence timing resolution (CTR) from two Cerenkov radiator integrated microchannel plate photomultiplier tubes (CRI-MCP-PMTs) was conducted with the CD-DSM TDCs for sub-100 ps timing measurements. A comparison with current-edge TDCs further highlights the superior performance of the CD-DSM TDCs.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge