Piero Malcovati

The Sparse Readout RIGEL Application Specific Integrated Circuit for Pixel Silicon Drift Detectors in Soft X-Ray Imaging Space Applications

Apr 27, 2022

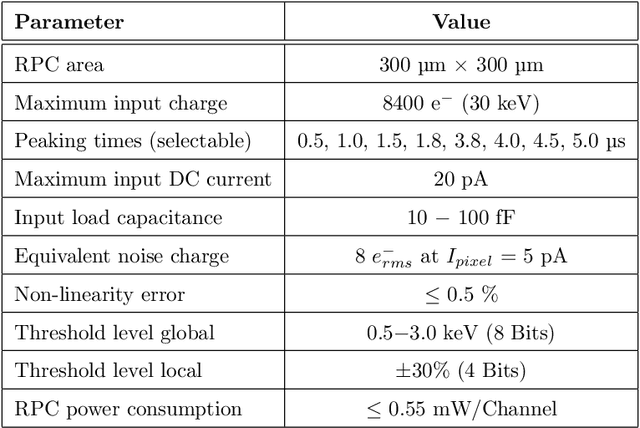

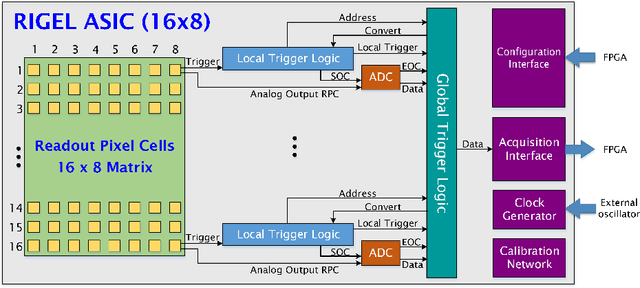

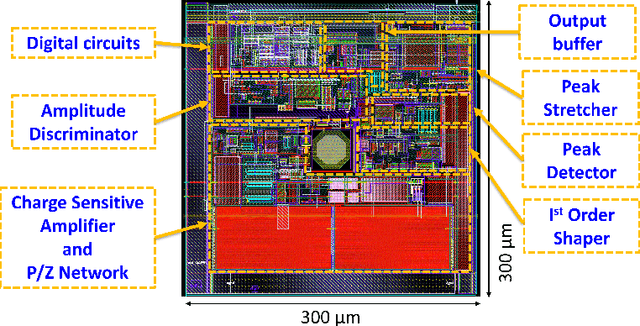

Abstract:An Application Specific Integrated Circuit (ASIC), called RIGEL, designed for the sparse readout of a Silicon Pixel Drift Detector (PixDD) for space applications is presented.The low leakage current (less than 1 pA at +20 {\deg}C) and anode capacitance (less than 40 fF) of each pixel (300 um x 300 um) of the detector, combined with a low-noise electronics readout, allow to reach a high spectroscopic resolution performance even at room temperature. The RIGEL ASIC front-end architecture is composed by a 2-D matrix of 128 readout pixel cells (RPCs), arranged to host, in a 300 um-sided square area, a central octagonal pad (for the PixDD anode bump-bonding), and the full-analog processing chain, providing a full-shaped and stretched signal. In the chip periphery, the back-end electronics features 16 integrated 10-bits Wilkinson ADCs, the configuration register and a trigger management circuit. The characterization of a single RPC has been carried out whose features are: eight selectable peaking times from 0.5 us to 5 us, an input charge range equivalent to 30 keV, and a power consumption of less than 550 uW per channel. The RPC has been tested also with a 4x4 prototype PixDD and 167 eV Full Width at Half Maximum (FWHM) at the 5.9 keV line of 55Fe at 0{\deg}C and 1.8 us of peaking time has been measured.

An early shutdown circuit for power reduction in high-precision dynamic comparators

Oct 05, 2021

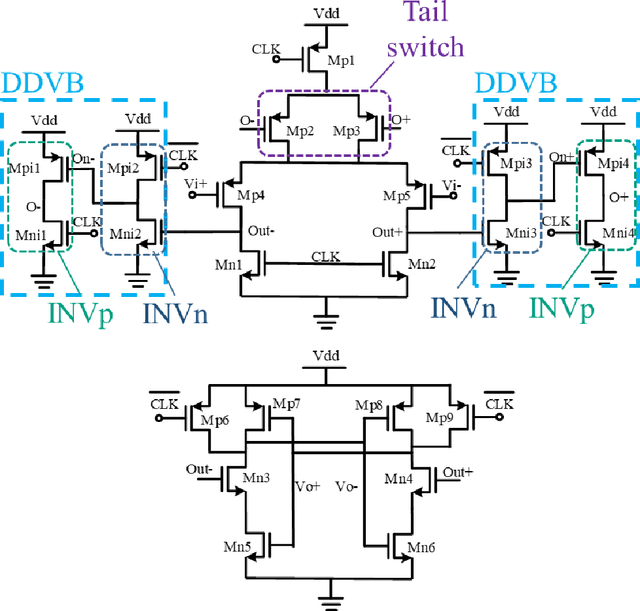

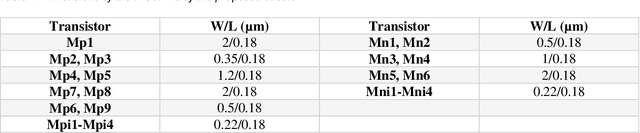

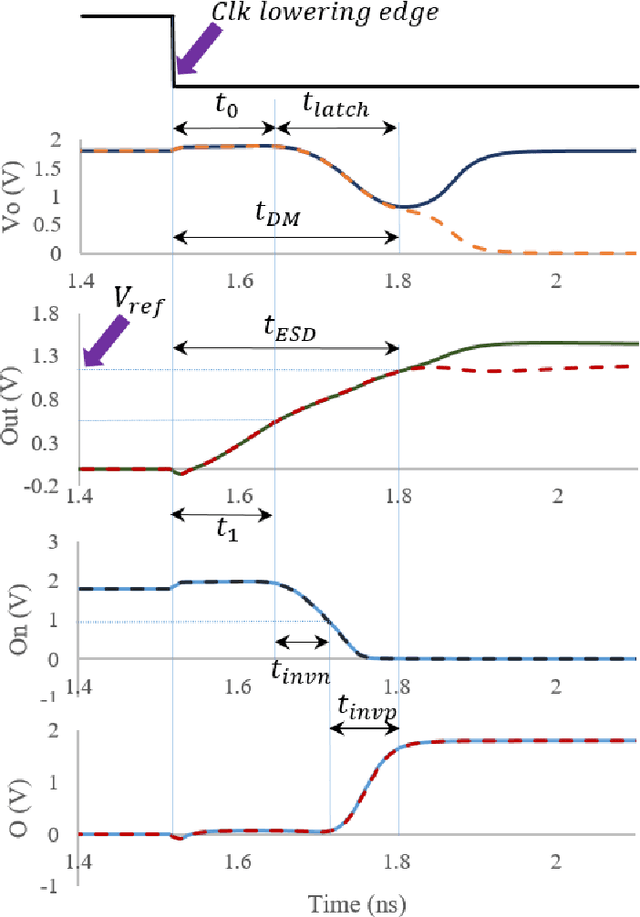

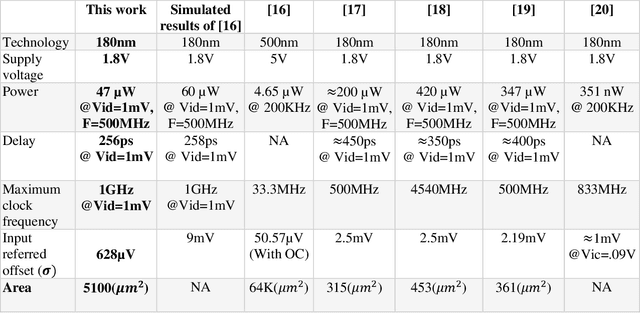

Abstract:Dynamic comparators are an essential part of low-power analog to digital converters (ADCs) and are referred to as one of the most important building blocks in mixed mode circuits. The power consumption and accuracy of dynamic comparators directly affects the overall power consumption and effective number of bits of the ADC. In this paper, an early shutdown approach is proposed to deactivate the first stage preamplifier at the suitable time. Furthermore, a time domain offset cancellation technique is incorporated to reduce offset effects. With the proposed method power consumption can be reduced in low power high precision dynamic comparators. The proposed method has been simulated in a standard 0.18{\mu}m CMOS technology and the results confirm its effectiveness. The proposed circuit has the ability of reducing the power consumption by 21.7% in the worst case, while having little effect on the speed and accuracy in comparison with the conventional methods. The proposed comparator consumes only 47{\mu}W while operating at 500MHz. Furthermore, Monte Carlo evaluations showed that the standard deviation of the residual input referred offset was 620{\mu}V.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge