Mohammad-Hossein Moaiyeri

CNFET-based design of efficient ternary half adder and 1-trit multiplier circuits using dynamic logic

Oct 05, 2021

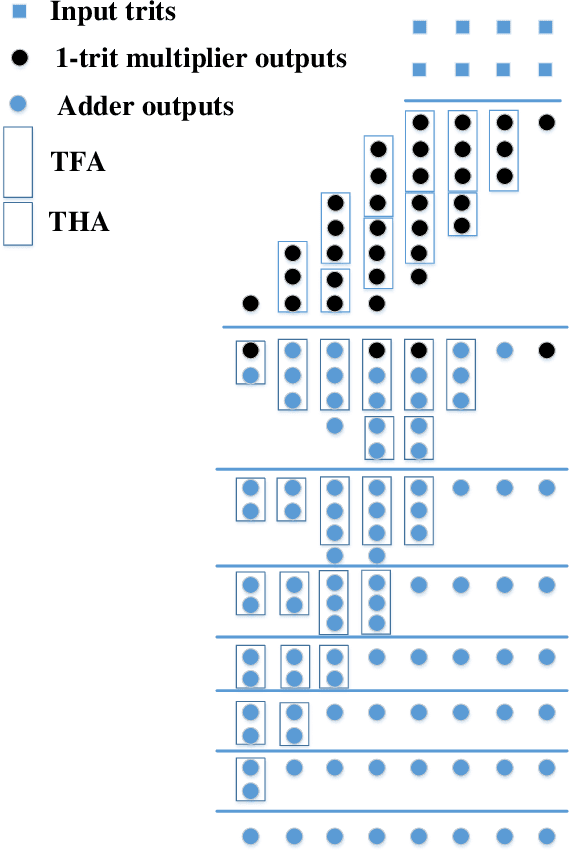

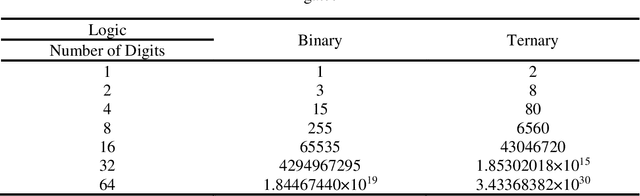

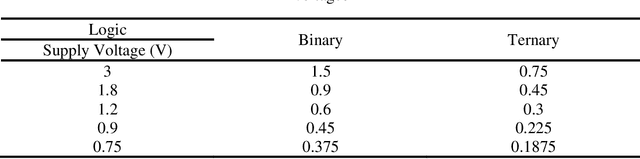

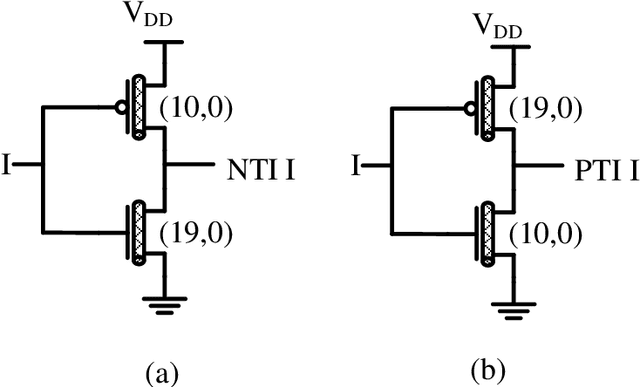

Abstract:This paper presents a ternary half adder and a 1-trit multiplier using carbon nanotube transistors. The proposed circuits are designed using pass transistor logic and dynamic logic. Ternary logic uses less connections than binary logic, and less voltage changes are required for the same amount of data transmission. Carbon nanotube transistors have advantages over MOSFETs, such as the same mobility for electrons and holes, the ability to adjust the threshold voltage by changing the nanotube diameter, and less leakage power. The proposed half adder has lower power consumption, delay, and fewer transistors compared to recent ternary half adders that use similar design methods. The proposed 1-trit multiplier also has a lower delay than other designs. Moreover, these advantages are achieved over a wide supply voltage range, operating temperatures, and output loads. The design is also more robust to process variations than the nearest design in terms of PDP.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge