Quantifying the Capacity Gains in Coarsely Quantized SISO Systems with Nonlinear Analog Operators

Paper and Code

Aug 08, 2022

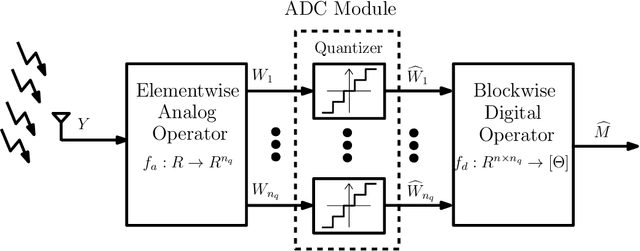

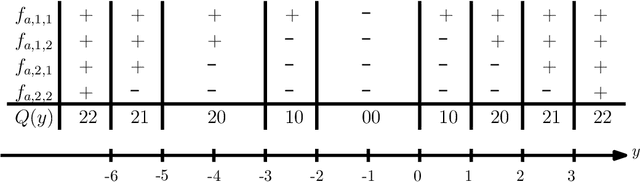

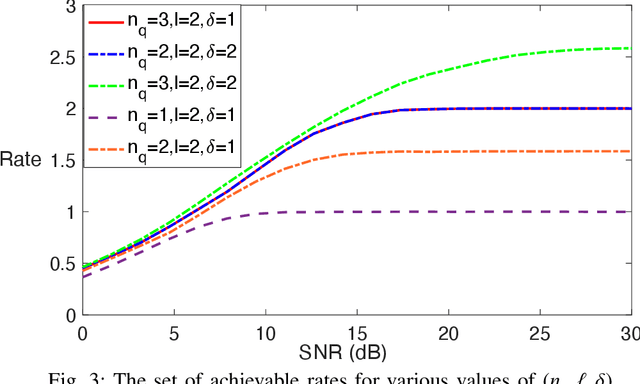

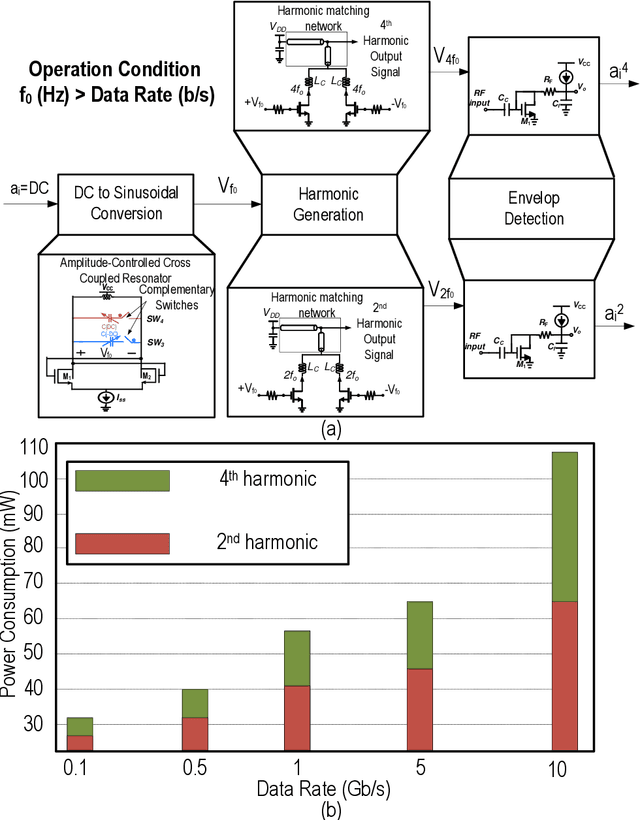

The power consumption of high-speed, high-resolution analog to digital converters (ADCs) is a limiting factor in implementing large-bandwidth mm-wave communication systems. A mitigating solution, which has drawn considerable recent interest, is to use a few low-resolution ADCs at the receiver. While reducing the number and resolution of the ADCs decreases power consumption, it also leads to a reduction in channel capacity due to the information loss induced by coarse quantization. This implies a rate-energy tradeoff governed by the number and resolution of ADCs. Recently, it was shown that given a fixed number of low-resolution ADCs, the application of practically implementable nonlinear analog operators, prior to sampling and quantization, may significantly reduce the aforementioned rate-loss. Building upon these observations, this work focuses on single-input single-output (SISO) communication scenarios, and i) characterizes capacity expressions under various assumptions on the set of implementable nonlinear analog functions, ii) provides computational methods to calculate the channel capacity numerically, and iii) quantifies the gains due to the use of nonlinear operators in SISO receiver terminals. Furthermore, circuit-level simulations, using a 65 nm Bulk CMOS technology, are provided to show the implementability of the desired nonlinear operators in the analog domain. The power requirements of the proposed circuits are quantified for various analog operators.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge