Non-sequential Division

Paper and Code

May 12, 2021

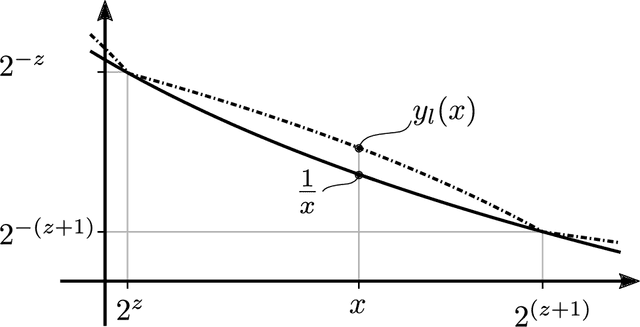

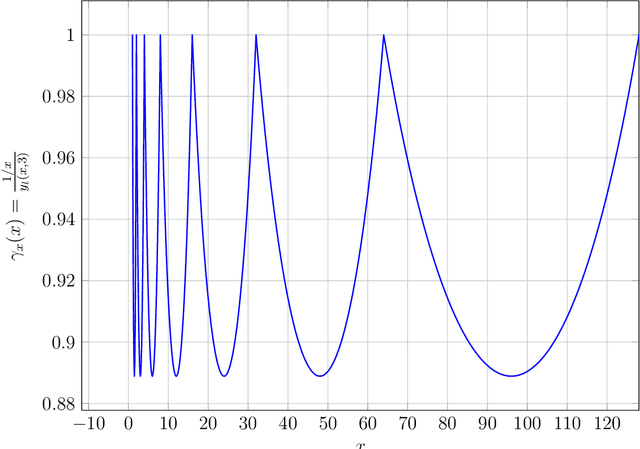

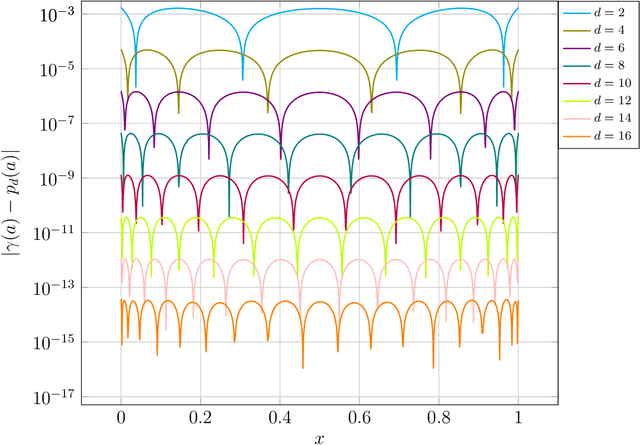

The division operation is important for many areas of data processing. Especially considering today's demand for hardware accelerators for machine learning algorithms, there is a high demand for an efficient calculation of the division function, e.g. for averaging operations or the online calculation of activation functions. For such algorithms, which are often iterative in nature, one would like to have a non-sequential way of calculating the division operation. The work presents such an approach. It is based on an efficient way of calculating the reciprocal operation, based on a low complexity approximation combined with a correction function. The described approach allows approximating the division operation (with errors that can be made arbitrarily low), within one clock cycle using only low hardware requirements (although one might reasonably use more clock cycles to increase the clock frequency). These hardware requirements are scale-able depending on the desired precision. We show results obtained by synthesis and hardware simulations demonstrating the low complexity and high clock speed achievable with the described method.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge