Design and Implementation a 8 bits Pipeline Analog to Digital Converter in the Technology 0.6 μm CMOS Process

Paper and Code

Aug 04, 2008

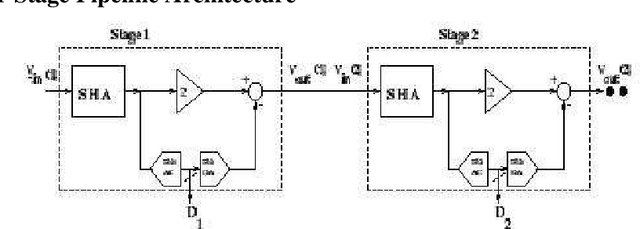

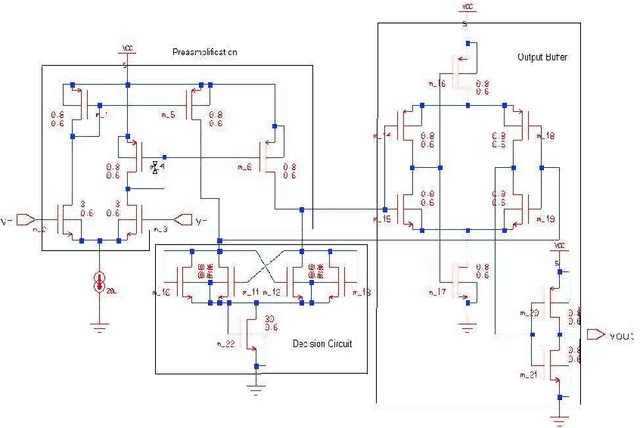

This paper describes a 8 bits, 20 Msamples/s pipeline analog-to-digital converter implemented in 0.6 \mu m CMOS technology with a total power dissipation of 75.47 mW. Circuit techniques used include a precise comparator, operational amplifier and clock management. A switched capacitor is used to sample and multiplying at each stage. Simulation a worst case DNL and INL of 0.75 LSB. The design operate at 5 V dc. The ADC achieves a SNDR of 44.86 dB. keywords : pipeline, switched capacitor, clock management

* 5 pages, Conference in Paris

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge