A signed pulse-train based image processor-array for parallel kernel convolution in vision sensors

Paper and Code

Oct 05, 2021

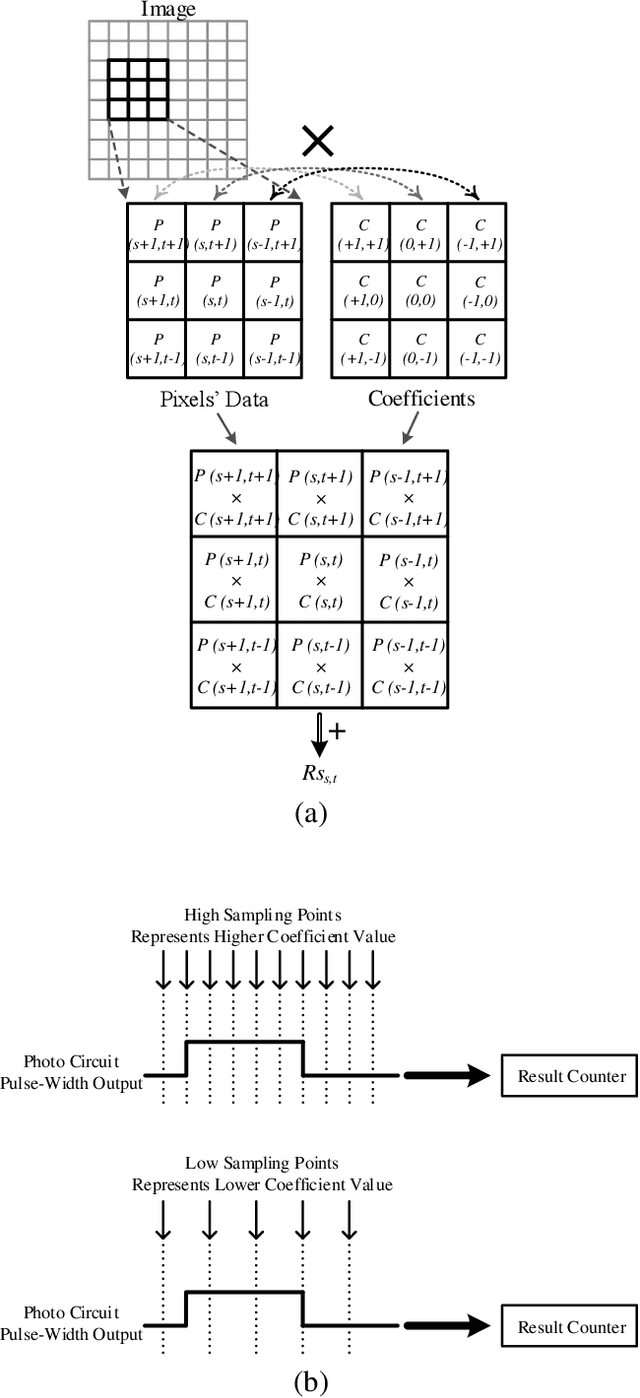

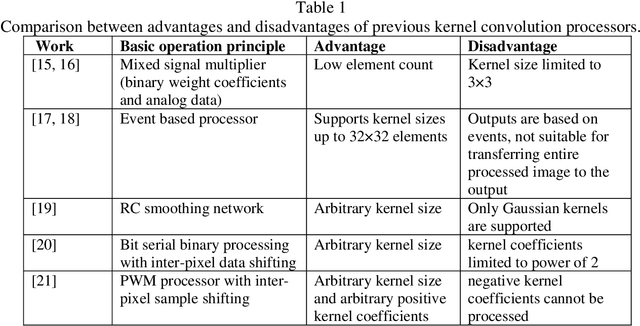

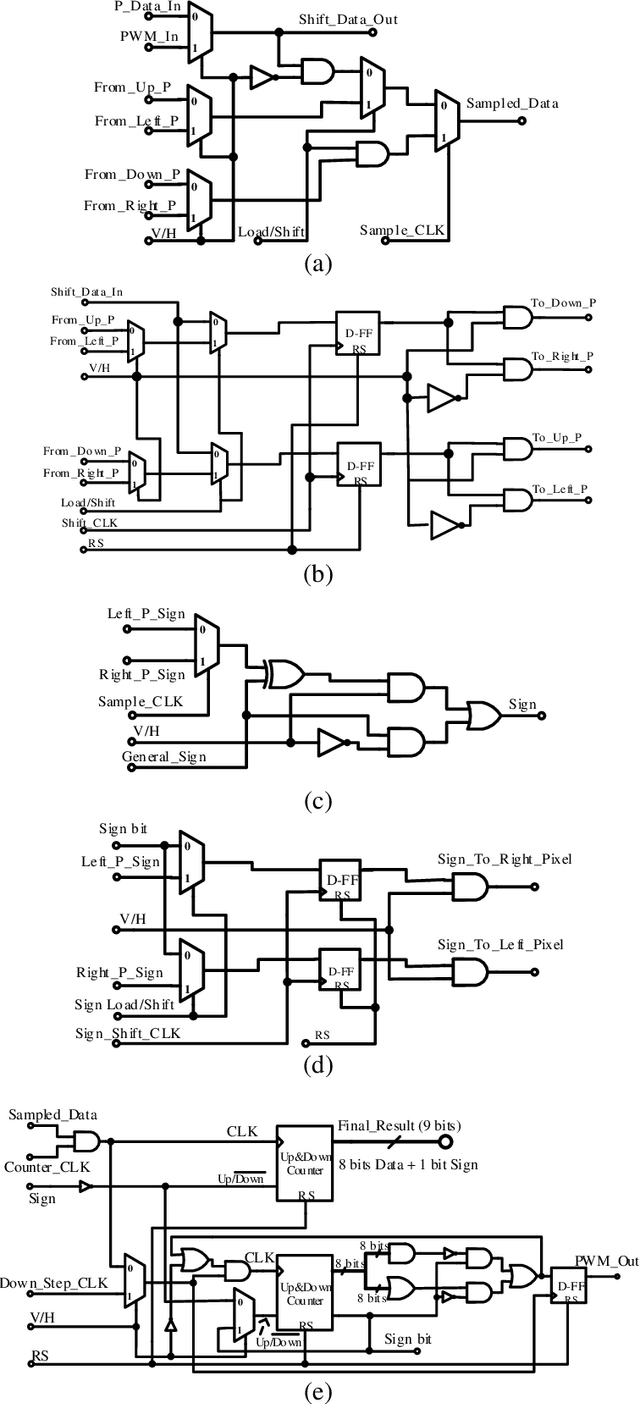

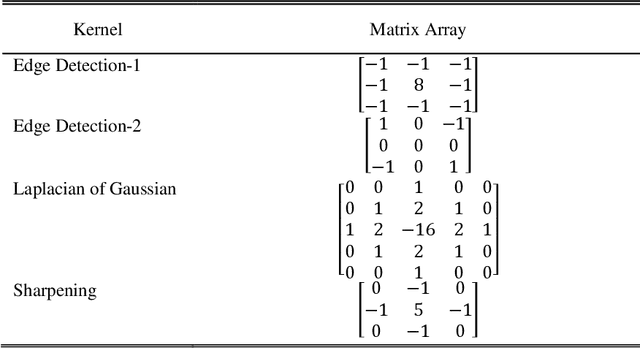

Purpose- High speed image processing is a challenging task for real-time applications such as product quality control of manufacturing lines. Smart image sensors use an array of in-pixel processors to facilitate high-speed real-time image processing. These sensors are usually used to perform the initial low-level bulk image filtering and enhancement. Design- In this paper, using pulse-width modulated signals and regular nearest neighbor interconnections, a convolution image processor is presented. The presented processor is not only capable of processing arbitrary size kernels, but the kernel coefficients can be any arbitrary positive or negative floating number. Findings- The performance of the proposed architecture is evaluated on a FPGA platform. The peak signal-to-noise ratio (PSNR) metric is used to measure the computation error for different images, filters, and illuminations. Finally, the power consumption of the circuit in different operation conditions is presented. Originality/Value- The presented processor array can be used for high speed kernel convolution image processing tasks including arbitrary size edge detection and sharpening functions which require negative and fractional kernel values.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge