Daiki Otaki

Nagaoka University of Technology, Niigata, Japan

Machine learning thermal circuit network model for thermal design optimization of electronic circuit board layout with transient heating chips

Aug 28, 2020

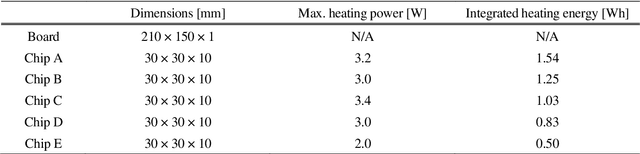

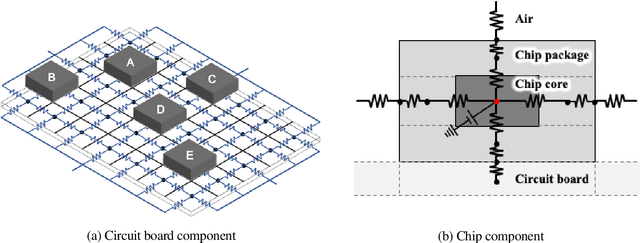

Abstract:This paper describes a method combining Bayesian optimization (BO) and a lamped-capacitance thermal circuit network model that is effective for speeding up the thermal design optimization of an electronic circuit board layout with transient heating chips. As electronic devices have become smaller and more complex, the importance of thermal design optimization to ensure heat dissipation performance has increased. However, such thermal design optimization is difficult because it is necessary to consider various trade-offs associated with packaging and transient temperature changes of heat-generating components. This study aims to improve the performance of thermal design optimization by artificial intelligence. BO using a Gaussian process was combined with the lamped-capacitance thermal circuit network model, and its performance was verified. As a result, BO successfully found the ideal circuit board layout that particle swarm optimization (PSO) and genetic algorithm (GA) could not. The CPU time for BO was 1/20 of that for PSO and GA. In addition, BO found a non-intuitive optimal solution in approximately 7 min from 10 million layout patterns. It was estimated that this was 1/1000 of the CPU time required for analyzing all layout patterns.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge